'1LT8'

# CLARKE - CPU/LCD DRIVER/MEMORY CONTROLLER

## External Reference Specification

Revision A

HEWLETT-PACKARD COMPANY

Preston Brown Dennis Engelbrecht

February 8, 1990

< COMPANY CONFIDENTIAL >

A-1LT8-0601-1

#### CONTENTS

| INTROL                   | DUCTION                                |                                                                         | 1                    |

|--------------------------|----------------------------------------|-------------------------------------------------------------------------|----------------------|

| BLOCK                    | DIAGRAM.                               |                                                                         | 2                    |

| 3.1                      | PIN Desc                               | ription                                                                 | 3<br>3<br>5          |

| SYSTEM<br>4.1            | Bus Stru<br>4.1.1<br>4.1.2<br>4.1.3    | Icture<br>General Protocol 7<br>Bus Commands 7<br>Command Auto-Switch 9 | 6<br>6               |

| 4.2                      | Addressi<br>4.2.1                      | Dummy Strobe 9<br>.ngSoft Configuration 10<br>Hard Configuration 11     | 9                    |

| 4.3<br>4.4<br>4.5<br>4.6 | Data Tra<br>Wait<br>Shutdowr           | nsfer1<br>                                                              | .1<br>.2<br>.2<br>.3 |

| 5.1                      | INTRODUC<br>ARCHITEC<br>5.2.1<br>5.2.2 | TION 1                                                                  | .4<br>.4<br>.4       |

| 5.3                      | 5.2.5<br>INSTRUCT<br>5.3.1<br>5.3.2    | HEX/DEC Modes 20<br>CION SET                                            | 20                   |

| 5.4                      | INTERRUP<br>5.4.1                      |                                                                         | 0                    |

| 5.5                      |                                        |                                                                         | 4                    |

| 5.6   | 5.5.8 Hardware Options 49<br>1LT8 CPU/1LK7 DIFFERENCES | 50 |

|-------|--------------------------------------------------------|----|

| SATU  | RN BUS INTERFACE                                       | 52 |

| 6.1   | Device IDs                                             | 52 |

| 6.2   | Control Addressing                                     | 53 |

| MEMOR | RY INTERFACE                                           | 55 |

| 7.1   | Configuration                                          | 55 |

| 7.2   | Getting MA[18]                                         | 56 |

| 7.3   | Using a Saturn bus device                              | 56 |

| 7.4   | Write Disable                                          | 56 |

| 7.5   | Memory Operations                                      | 56 |

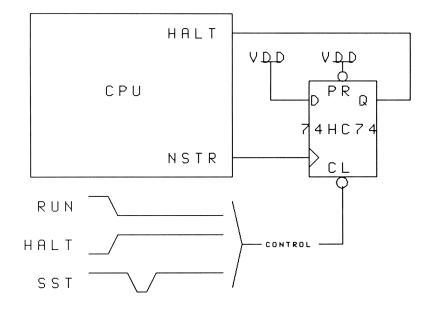

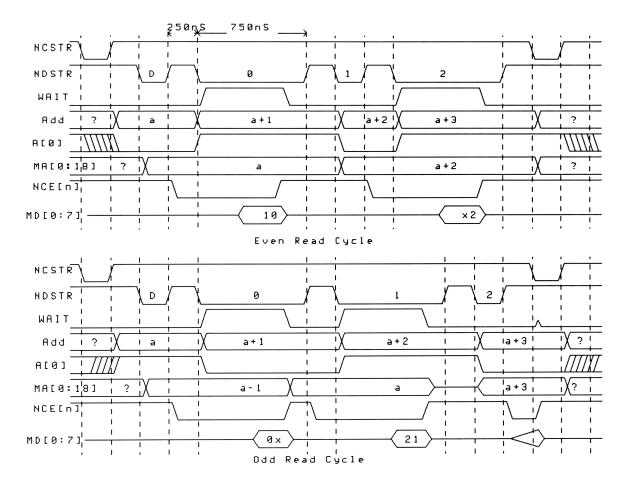

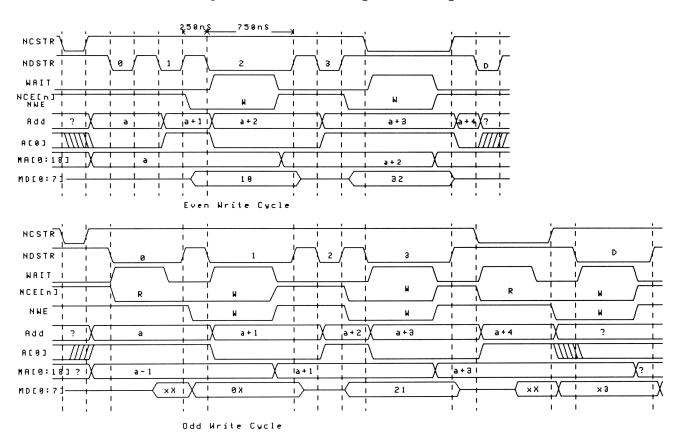

| 7.6   | Timing Diagrams                                        | 57 |

| 7.7   | Keyboard Operation                                     | 59 |

| 7.8   | Special Considerations                                 | 59 |

|       |                                                        |    |

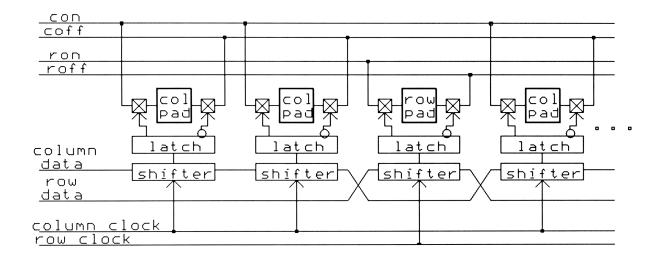

|       | DRIVER                                                 | 60 |

| 8.1   | Display Memory                                         | 61 |

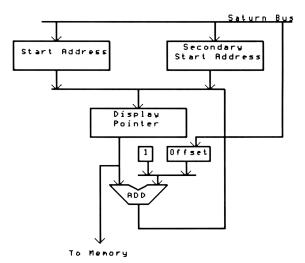

| 8.2   | Display Pointers                                       | 61 |

|       | 8.2.1 Display Start Address 62                         |    |

|       | 8.2.2 Display Line Offset 62                           |    |

|       | 8.2.3 Display Line Counter 63                          |    |

|       | 8.2.4 Display Secondary Start Address 63               |    |

| 8.3   | Control Registers                                      | 64 |

|       | 8.3.1 Display Bit Offset and DON 64                    |    |

|       | 8.3.2 Contrast Control 64                              |    |

|       | 8.3.3 Display Test 64                                  |    |

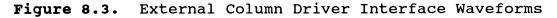

| 8.4   | External Column Driver Interface                       | 65 |

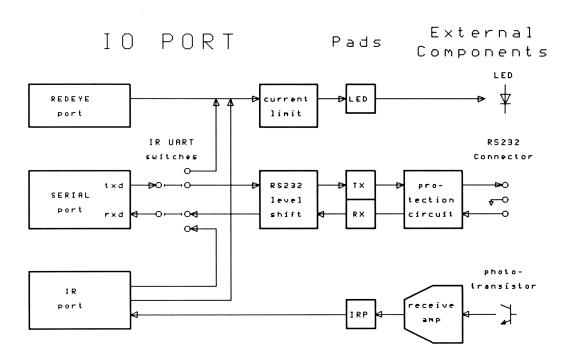

| τ/ο ι | PORTS                                                  | 66 |

| 9.1   | SERIAL PORT                                            | 67 |

| ~•±   | 9.1.1 Serial Format 67                                 | 57 |

|       | 9.1.2 RBR - Receive Buffer Register 68                 |    |

|       | 9.1.3 RCS - Receive Control/Status Register 68         |    |

|       | 9.1.4 CRER - Clear RER address 68                      |    |

|       | 9.1.5 TBR - Transmit Buffer Register 68                |    |

|       | -                                                      |    |

|       |                                                        |    |

|       | 9.1.7 IOC - Serial I/O Control Register 69             |    |

|       | 9.1.8 BAU - Baud Rate Register/Generator 70            |    |

|       | 9.1.9 Receiver Operation 70                            |    |

|       | 9.1.10 Transmitter Operation 72                        | _  |

| 9.2   | REDEYE (LED) PORT                                      | 73 |

|       | 9.2.1 REDEYE format 73                                 |    |

|       | 9.2.2 LCR - Led Control Register 74                    |    |

|       | 9.2.3 LBR - Led Buffer Register 74                     |    |

|       | 9.2.4 Operation 74                                     |    |

|       | 9.2.5 Special Considerations 75                        |    |

| 9.3   | IR PORT                                                | 75 |

|       | 9.3.1 IR format 76                                     |    |

|       | 9.3.2 IRC - IR Control Register 76                     |    |

|       |                                                        |    |

| 9.4                                                    | 9.3.3 Operation 76<br>IR UART MODE<br>9.4.1 IR UART Transmitter Operation 77<br>9.4.2 IR UART Receiver Operation 77 | 76                                     |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| TIMER<br>10.1<br>10.2                                  | Timer Control<br>Special Considerations                                                                             | 79<br>79<br>79                         |

| ANNUN                                                  | CIATORS                                                                                                             | 80                                     |

| CYCLIO<br>12.1                                         | C REDUNDANCY CHECK<br>Examples                                                                                      | 81<br>82                               |

| CARD I<br>13.1<br>13.2<br>13.3                         | DETECT<br>Card Detect Register<br>Other Applications<br>Special Considerations                                      | 83<br>83<br>84<br>84                   |

| SCRAT                                                  | CH PAD                                                                                                              | 85                                     |

| SERVI                                                  | CE REQUEST REGISTER                                                                                                 | 86                                     |

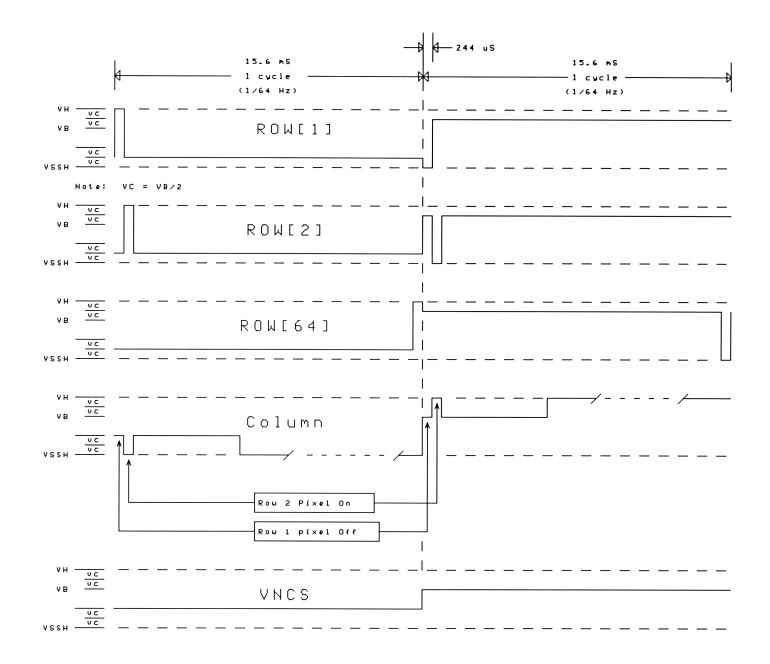

| ANALOO<br>16.1<br>16.2<br>16.3<br>16.4                 | G CIRCUITRY<br>Power Supply<br>Oscillator<br>Low Power Detection<br>LCD Drive Voltages                              | 87<br>87<br>88<br>88<br>90             |

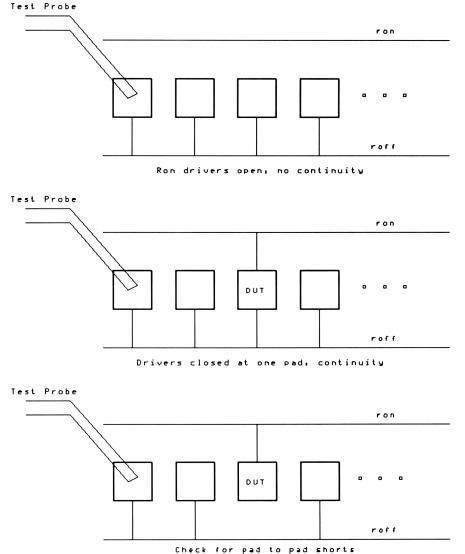

| TESTII<br>17.1<br>17.2<br>17.3<br>17.4<br>17.5<br>17.6 | NG<br>Mode Register<br>Mode Programming<br>CPU Scan Path<br>Display Testing<br>Power Isolation Circuit.<br>Burn-In  | 92<br>92<br>93<br>93<br>94<br>97<br>97 |

### LIST OF FIGURES

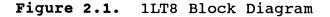

| Figure 2.1.  | 1LT8 Block Diagram                         | 2  |

|--------------|--------------------------------------------|----|

| Figure 3.1.  | Pin Out                                    | 5  |

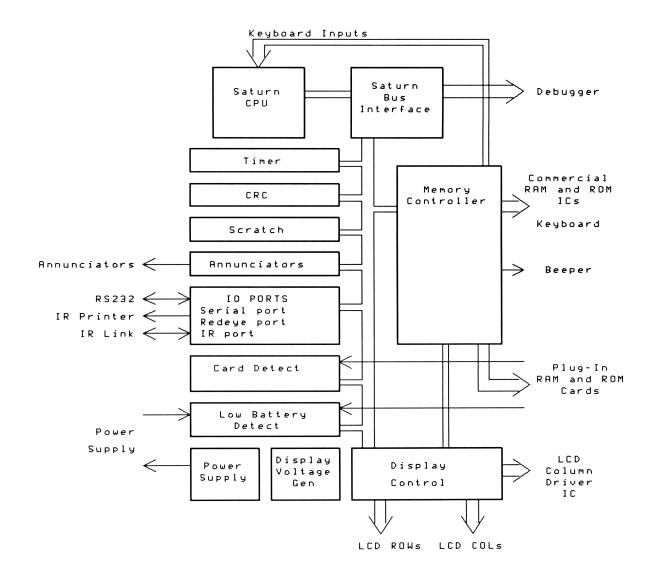

| Figure 5.1.  | CPU Register Set                           | 15 |

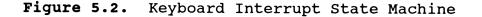

| Figure 5.2.  | Keyboard Interrupt State Machine           | 43 |

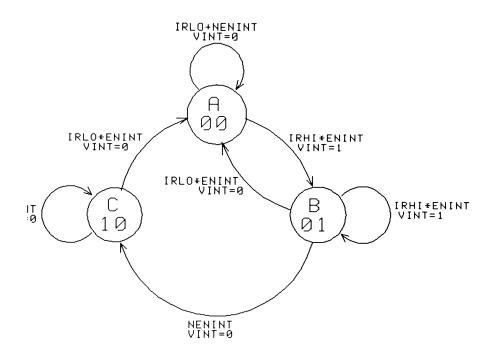

| Figure 5.3.  | CPU Single-Step Circuit                    | 47 |

| Figure 7.1.  | Memory Read Cycle                          | 57 |

| Figure 7.2.  | Memory Write Cycle                         | 58 |

| Figure 8.1.  | LCD Drivers                                | 60 |

| Figure 8.2.  | Pointer Hardware Block Diagram             | 62 |

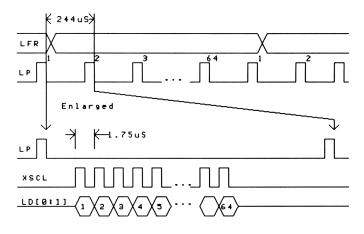

| Figure 8.3.  | External Column Driver Interface Waveforms | 65 |

| Figure 9.4.  | IO PORT                                    | 66 |

| Figure 16.1. | LCD drive waveforms                        | 91 |

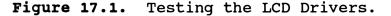

| Figure 17.1. | Testing the LCD Drivers                    | 96 |

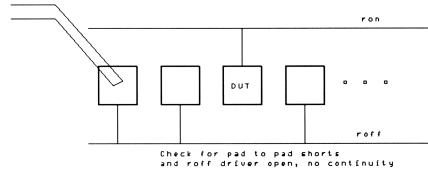

| Figure 17.2. | Power Isolation Circuit                    | 97 |

#### CHAPTER 1 INTRODUCTION

This document contains a description of the '1LT8' IC. This chip is designed as the single custom chip in the Charlemagne calculator. The chip also supports a commercial bus interface that can be used to drive up to 5 commercial memory ICs or ports. The '1LT8' IC is divided into the following functional areas:

- 1. A 4-bit CPU. The CPU operates on the Saturn bus and is 100% object code compatible with the 1LF2 and 1LK7 CPU's.

- 2. A MEMORY CONTROLLER capable of interfacing to 5 commercial RAMs, ROMs, or plug-in ports.

- 3. A Liquid Crystal Display (LCD) DRIVER capable of driving a 64-way multiplexed display.

- 4. A 32 bit, quartz-crystal controlled TIMER.

- 5. A 1200-9600 baud full-duplex UART capable of driving RS232 or infrared level signals.

- 6. A IR LED driver with built-in REDEYE formatting and pacing.

- 7. A collection of ANALOG CIRCUITRY including: Power Supply; Low Battery Indicator (LBI); Power-on Reset (POR) circuit; Crystal Oscillator; Frequency Multiplier; and Display Voltage Generation.

A chapter has been dedicated to each of these functional areas. Also included are chapters describing the BLOCK DIAGRAM and PIN OUT of the chip.

1LT8 is a highly leveraged IC based on the LEWIS design. The major differences are outlined below:

- 1. 1LT8 has no built in ROM; and the LEWIS mask options were also removed.

- The display bit map is not built into the IC, but is contained in external RAM. The bit map ordering has changed.

- 3. 1LT8 requires one or two external LCD column drivers.

#### CHAPTER 2 BLOCK DIAGRAM

The following is a simplified block diagram of the 1LT8 chip.

#### CHAPTER 3 PIN OUT

## 3.1 **PIN Description**

This chapter gives a brief description of each pin's function.

PIN # DESCRIPTION

Power Supplies:

| VDD     | 1 | Power Supply: 4 to 5.5 Volts.                              |

|---------|---|------------------------------------------------------------|

| GND     | 4 | 0 Volts.                                                   |

| TGND    | 1 | Burn-in Ground; isolated from GND by a diode and resistor. |

| VH      | 1 | Most positive display voltage : VDD to 9 volts.            |

| VSSH    | 1 | Most negative display voltage : GND to VDD                 |

| VCO     | 1 | Card power = VDD when CPU is running.                      |

| VB[0:2] | 3 | Battery voltage inputs.                                    |

Power supply generation:

| PMP | 1 | Power-sup          | ply   | connec | ction | to | b the  | gate | e of  | an  |

|-----|---|--------------------|-------|--------|-------|----|--------|------|-------|-----|

|     |   | external inductor. | trans | sistor | used  | to | charge | the  | exter | nal |

DIODE 1 A p-channel device from this pin to VDD is used to discharge the inductor into the VDD supply.

Display:

| LC[1:4]  | 4  | Display Columns.                               |

|----------|----|------------------------------------------------|

| LR[1:64] | 64 | Display Rows.                                  |

| LA[1:6]  | 6  | Annunciator (non-multiplexed segment) drivers. |

| LN       | 1  | Common (Row) line for Annunciators.            |

A-1LT8-0601-1

< HP CONFIDENTIAL >

Interface to external display drivers:

- LD[0:1] 2 Data output to external display drivers, synchronized to XSCL.

- XSCL 1 Clock output.

- LP 1 Latch output pulse.

- LFR 1 Frame clock output, sets driver polarity.

- VNCS 1 Column non-select voltage.

Saturn Bus:

| NSTR     | 1     | NOT STROBE; System clock, active low.                                                                            |

|----------|-------|------------------------------------------------------------------------------------------------------------------|

| NCD      | 1     | NOT COMMAND-DATA; low during NSTR for a command,<br>high for data.                                               |

| BUS[0:3] | 4     | 4 bit multiplexed address, data, and command bus.                                                                |

| WAIT     | 1     | Wait input; causes CPU to wait with NSTR low;<br>for slow devices.                                               |

| HALT     | 1     | When asserted high, the CPU completes the current instruction, tristates the BUS, NSTR, and NCD lines and waits. |

| Memory   | Contr | oller:                                                                                                           |

| MA[0:17] | 18    | Address lines, aliased as IR[0:8], OR[0:8]<br>(Keyboard I/O)                                                     |

| MD[0:7]  | 8     | Data lines.                                                                                                      |

| NCE[1]   | 1     | ROM chip enable, read operations only.                                                                           |

| NCE[2:3] | 2     | RAM or ROM Chip enables; active low. NCE[3] can<br>also be mapped to NOT MA[18] by setting the DA19<br>bit.      |

| CE[1:2]  | 2     | Card enables; active high.                                                                                       |

| NWE      | 1     | Read/Write Control output; active low.                                                                           |

| NOE      | 1     | Card output enable; active low.                                                                                  |

| CDT[1•2] | C     | Card Datast inputs, sansas NUDOUT (Write protect                                                                 |

CDT[1:2] 2 Card Detect inputs; senses NWPOUT (Write protect output) of plug-in cards. High indicates card present and writable, Low indicates card present and write protected, Float indicates that no card is present. If a card is inserted or removed the CPU is interrupted and HS3 is set.

#### Other:

| NRES      | 1 | Reset; active low input.              |

|-----------|---|---------------------------------------|

| ON        | 1 | On Key; drives the CPU signal IR15X.  |

| BEEP      | 1 | Beeper Driver, high voltage (VH) OR11 |

| LED       | 1 | LED output driver.                    |

| IRI       | 1 | Infrared I/O input pin.               |

| RX,TX     | 2 | Serial I/O.                           |

| XIN, XOUT | 2 | Quartz crystal connections.           |

TOTAL 147

#### 3.2 Package

1LT8 is packaged in a TAB package with outer leads and size identical to the LEWIS TAB package. The inner leads have changed to allow 1LT8 to have 147 pins in a reasonable die size of nnnn by sorrynnnnons. The following figure gives the pin-out of the package. The TAB package includes 166 pins on a 20 mil pitch.

#### Figure 3.1. Pin Out

| NC                                                                                                                                                                                       | B S N C C C C D D F P S X N X H E M C C D I N E O MA[1] -<br>0 S C 1 2 3 4 1 0 R C D E P E O D O D D E MA[2] -<br>H S L P 1 D MA[3] -<br>E MA[4] -<br>MA[5] -<br>MA[6] -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -LR36<br>-LR34<br>-LR34<br>-LR33<br>-LR1<br>-LR3<br>-LR3<br>-LR3<br>-LR5<br>-LR7<br>-LR6<br>-LR7<br>-LR10 LL L<br>-LR10 LL L<br>-LR11 R R G R<br>-LR12 1 1 N 1<br>-LR13 5 6 D 7<br>-LR14 | MHL 12] -<br>MAC 13] -<br>MAC 14] -<br>MAC 14] -<br>MAC 15] -<br>MAC 15] -<br>MAC 16] -<br>MD [0] -<br>MD [0 |  |

#### CHAPTER 4 SYSTEM BUS DESCRIPTION

This chapter is a generalized discussion of the 1LT8 system bus. The 1LT8 chip includes a CPU and several peripheral devices. The communication between the CPU and on-chip devices is the same as for external devices except that the communication between the CPU and on-chip devices is not driven onto the external bus unless the chip is in VERBOSE mode. See the section on "Device Modes" in the chapter entitled "TESTING" for a full discussion of when the external bus is active.

The 1LT8 CPU is functionally compatible with the LEWIS CPU. This chapter describes the 1LT8 CPU system bus structure, protocol, and timing. Also included is a description of the bus commands, device addressing, and the power down and wakeup characteristics. A description of the addressing and configuration of specific onchip devices is found in the chapter entitled "SATURN BUS INTERFACE".

#### 4.1 Bus Structure

The 1LT8 CPU bus consists of 6 lines including:

- 4 BUS[0:3] data lines, driven by the CPU or system devices.

- 1 NSTR driven by the CPU.

- 1 NCD usually driven by the CPU.

Soft configured peripheral chips have two additional lines:

- 1 DAISYIN (DIN) input to device

- 1 DAISYOUT (DOUT) output from device, may be tied to next device's DIN

An additional line may be used by slow peripherals:

1 WAIT - input to CPU

NOTE : A 'N' before a signal name denotes negative true logic.

Page 6

#### 4.1.1 General Protocol

NSTR is driven by the CPU and serves to synchronize all bus transfers. It is not a true system clock since it can remain inactive for several cycles while the CPU is performing internal manipulations. All address, data, and bus commands are transferred on the BUS[0:3]. The BUS[0:3] is driven during NSTR low by either the CPU or the device the CPU is accessing. This data is latched either by the CPU or by the receiving device on the rising edge of NSTR.

All bus operations are initiated by the CPU. The CPU starts a specific transfer on the bus by driving the NCD line low before NSTR goes low. While NCD and NSTR are low the CPU drives a bus command on the BUS[0:3] and all devices in the system latch the command on the rising edge of NSTR. This strobe is referred to as a command strobe. The bus command issued during a command strobe specifies the operation that is to be performed on each succeeding NSTR until another bus command is issued. At all times when data or address is being transferred NCD is held high. A strobe issued while NCD is high is referred to as a data strobe.

#### 4.1.2 Bus Commands

The bus commands are:

| COMMAND |         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                |

|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | NOP     | All devices ignore NSTR until a new command is loaded.                                                                                                                                                                                                                                                                                                                     |

| 1       | ID      | The unconfigured device that has its DAISY-IN<br>high sends its 5-nibble ID on the following<br>data strobes, starting with the low- order<br>nibble of the ID.                                                                                                                                                                                                            |

| 2       | PC READ | (PC)->BUS or read using the Program Counter<br>(PC). The device addressed by its program<br>counter sends data pointed to by its local<br>program counter on each following data strobe<br>and all devices increment their local program<br>counters once each data strobe. A dummy<br>strobe immediately follows the issuance of<br>this bus command (see Section 4.1.4). |

| 3       | DP READ | (DP)->BUS or read using the Data Pointer<br>(DP). The device addressed by its data<br>pointer sends data pointed to by its local<br>data pointer on each following data strobe and                                                                                                                                                                                         |

| A-1LT8-0601-1 < HP CONFIDENTIAL > Pag | е | 7 |  |

|---------------------------------------|---|---|--|

|---------------------------------------|---|---|--|

all devices increment their local data pointers once each data strobe. A dummy strobe immediately follows the issuance of this bus command (see Section 4.1.4).

- 4 SET MODE All data strobes following this command load data into the MODE register to set test modes. See Chapter 17 for details on test modes.

- 5 DP WRITE BUS->(DP) or write using DP. The device addressed by its data pointer loads the data on the following data strobes into the location pointed to by its local data pointer and all devices increment their local data pointer once each data strobe.

- 6 LOAD PC BUS->PC or load PC. All devices load the data on the following 5 data strobes into their local program counter, starting with the low-order nibble. After all 5 nibbles are transferred the command code is automatically changed to a 2, PC READ (see Section 4.1.3).

- 7 LOAD DP BUS->DP or load DP. All devices load the data on the following 5 data strobes into their local data pointer, starting with the low- order nibble. After all 5 nibbles are transferred the command code is automatically changed to a 3, DP READ (see Section 4.1.3).

- 8 CONFIGURE The unconfigured device that has its DAISY-IN high loads the following 5 data nibbles into its configuration register starting with the low-order nibble.

- 9 UNCONFIGURE The device currently addressed by its data pointer unconfigures itself. The device then responds to CONFIGURE and ID bus commands only. The local data pointers must be loaded immediately preceding an unconfigure command.

- A POLL All peripherals that require service pull one data line high during the next NSTR low (see Section 4.6).

- B Reserved This command is the same as NOP for the internal peripherals and is not issued by the CPU.

- C BUSCC The device currently addressed by its local data pointer performs a specific operation as

defined by the individual device. This command is the same as NOP for the internal peripherals and is not issued by the CPU.

- D Reserved This command is the same as NOP for the internal peripherals and is not issued by the CPU.

- E SHUTDOWN When the CPU has received a SHUTDN instruction it issues this command before shutting down. Each device responds based on its own special requirements to this command (see Section 4.5).

- F RESET All devices reset their configuration flags (if applicable) and perform other local resets based on their own special requirements.

#### 4.1.3 Command Auto-Switch

There exists one special case in which all devices change their current bus command. This is called 'auto-switch' and occurs following the load of either the PC or the DP. On the rising edge of NSTR after the 5th nibble of address has been loaded all devices clear bit 2 of their command latch changing the bus command from either a LOAD PC to PC READ or LOAD DP to DP READ.

#### 4.1.4 Dummy Strobe

Immediately following a PC READ bus command, a DP READ bus command, and a command auto-switch the CPU issues a 'dummy strobe'. This dummy strobe appears as a data strobe except that no data is transferred during this period and devices do not increment their local address registers. The dummy strobe provides memory devices a full strobe cycle for the first access and therefore allows data pipelining.

#### 4.2 Addressing

All bus peripherals have local auto-incrementing address pointers for accessing instructions or data. These local pointers are referred to as PC (program counter) and DP (data pointer). As their names imply, the PC is used for accessing instructions and the DP for data. To bus peripherals however, there is no distinction between the two. The CPU automatically updates (loads) these local pointers whenever necessary for instruction fetches or data transfers. Each bus peripheral is either hard addressed at a specific address (hard configured) or capable of being dynamically located within the address space (soft configured). A bus peripheral only responds to READ and WRITE commands if its local address register (PC or DP depending on the particular command) is within its configured address space.

All bus peripherals are designed so that the upper-order bits of the local address register can be compared with the upper-order bits of the device's configuration register (hard or soft). If these bits are identical, the device has an address match and will respond to read and write commands (and the unconfigure and BUSCC commands if applicable). Each device with a given address space size compares a given number of the upper-order bits of address. For example, a device with an address space size of 2K nibbles requires 11 bits of address leaving the upper 9 bits for its configuration register.

#### 4.2.1 Soft Configuration

A soft configured device powers up unconfigured. When unconfigured a device responds only to the ID and CONFIGURE commands and drives its DAISYOUT low. A device's ID code is used to identify the device before it is configured. If a soft configured device is unconfigured and has its DAISYIN line high, it sources its 5-nibble ID code starting with the low-order nibble on the 5 data strobes immediately following the issuance of an ID command (no dummy strobe is issued). The 5-nibble ID code contains information on the device type and the address space required by the device.

Since the BUS[0:3] is precharged low before each strobe, the CPU will read an ID of all zeros if all devices are configured (or are unconfigured but have DAISYIN low).

A soft configured device is assigned its address configuration by the CONFIGURE command. If an unconfigured device has its DAISYIN line high, it loads the configuration address that is issued on the 5 data strobes immediately following the CONFIGURE command (low-order nibble first) into its configuration register. A device may actually latch only the number of high-order bits it requires as determined by its address space size.

After being configured a device no longer responds to either an ID or CONFIGURE command. A configured device drives DAISYOUT to the same logic level as DAISYIN. The DAISYOUT of one device may be tied to the DAISYIN of second device. In this way many devices may be daisy-chained together in a way that they can be configured one at a time to different addresses. After being configured a device waits until the next command strobe to set its configuration flag in order to delay DAISYOUT so that the next device on the daisychain will not be configured simultaneously.

A device may be unconfigured by either a RESET or UNCONFIGURE bus command. The bus RESET command unconfigures all soft configured devices in the system. A device responds to an UNCONFIGURE command by clearing its configuration flag if the DP is within its address configuration.

A device DAISYIN may be tied to the CPU'S OR lines to provide software control over when that device will respond to ID, CONFIGURE, and UNCONFIGURE commands. When multiple soft configured devices are required they are typically chained together; DAISYOUT to DAISYIN.

#### 4.2.2 Hard Configuration

A hard configured device powers-up configured to a specific address. It will not respond to an ID, CONFIGURE, or UNCONFIGURE command and a bus RESET will not affect its configuration. If the device has a DAISYOUT, it is always driven to the same logic level as its DAISYIN.

#### 4.3 Data Transfer

All information that is transferred on the BUS[0:3] is latched on the rising edge of NSTR.

The CPU loads all devices' local address registers by issuing a LOAD PC or LOAD DP bus command followed by 5 data strobes of address, least significant nibble first. After the last nibble of address has been loaded all devices auto-switch to a PC READ or DP READ bus command. The CPU may then read the contents of that address location by issuing one dummy strobe followed by 1 to 16 data strobes during which the CPU latches the BUS[0:3] data. The CPU may read without first loading the local address registers by issuing a PC READ or DP READ, followed by a dummy strobe, followed by 1 to 16 data strobes. The CPU precharges the BUS[0:3] low each cycle before NSTR goes low. Therefore if no device responds the CPU reads zeros.

The CPU writes the contents of a specific addressed location similarly. It is not required to load the local address registers immediately before issuing a PC WRITE or DP WRITE command. The write command is followed by 1 to 16 data strobes during which the addressed device latches the BUS[0:3] data.

All devices increment their active address register (PC or DP) once each data strobe during read and write operations. It is

A-1LT8-0601-1

< HP CONFIDENTIAL >

Page 11

possible for a read or write operation to begin in one device and cross the address boundary into another device. In general, data transfers should not be limited to 16 nibbles.

Two other types of data transfers are ID, which is simply a 5nibble read with no address load or dummy strobe, and CONFIGURE, which is a 5-nibble write with no address load. Both these data transfers require that a device be unconfigured and that the DAISYIN line be high. POLL is a unique read and is discussed in Section 4.6.

#### 4.4 Wait

A slow peripheral device can cause the CPU to wait during a data strobe by driving WAIT high. While WAIT is high the CPU will hold NSTR low and will hold BUS[0:3] valid if a data nibble is being output. After WAIT goes low, the CPU will raise NSTR and latch BUS[0:3] if data is being input. Wait is resistively held low by the CPU. It should only be driven by a device if that device's address configuration matches the current address.

#### 4.5 Shutdown; Wakeup

The 1LT8 CPU can be shutdown under software control. The CPU executes a SHUTDN instruction by issuing a SHUTDOWN bus command and on the next cycle stopping the system clock (NSTR) and its own local oscillator. While in shutdown mode all data stored in CPU resident memory is preserved. The CPU is brought out of shutdown mode by either pulling an Input Register line high, or by driving NCD low in a special manner.

NCD is driven low to wake up the CPU primarily by a bus peripheral that needs service while the system is in shutdown mode. The peripheral must release NCD when the CPU begins an operation by driving NSTR low. If a peripheral wakes up the CPU and the CPU shuts down without satisfying its service request the device must not wake up the CPU again until its service request has been satisfied and it needs service again. This prevents a situation where the operating system does not know how to handle a device's service request and therefore cannot shutdown. For more information on power down and wake up see Section 5.3.2.

#### 4.6 Service Poll

If a device needs service while the CPU is operating it must wait until the CPU executes a service request instruction (SREQ), or, if it has the capability, interrupt the CPU. The SREQ instruction causes the CPU to issue a POLL bus command followed by one data strobe during which the CPU latches the BUS[0:3] data in the manner of a usual read. A device may respond to the service POLL by pulling one of the BUS[0:3] lines high. Since the CPU precharges the BUS[0:3] low every cycle before NSTR goes low the data read by the CPU is a binary OR of all devices' responses.

#### CHAPTER 5 1LT8 CPU

#### 5.1 INTRODUCTION

The 1LT8 CPU is identical to the SACAJAWEA/LEWIS CPU which is a leveraged redesign of the 1LK7 CPU. This CPU provides faster instruction execution times but still maintains full compatibility with the 1LF2/1LK7 and the HP-71B bus architecture.

The CPU internal and external data paths are 4 bits wide. Memory is accessed in 4-bit quantities (referred to as nibbles) using 20 bit addresses yielding a physical address space of 512K bytes. The CPU internal word size is 64-bits. Operations are performed on data strings up to 16 nibbles in length.

Section 5.6 is a summary of differences between the 1LT8 CPU and the 1LK7 for those already familiar with the 1LK7.

#### 5.2 ARCHITECTURE

#### 5.2.1 CPU Overview

The 1LT8 CPU is a proprietary CPU optimized for high-accuracy BCD math and low power consumption.

Operations performed by the 4-bit ALU include ADD, SUBTRACT, AND OR, and ones, twos, nines and tens complements. A shifter allows bit-shift, nibble-shift and nibble rotate. The CPU internal word size is 64-bits (16 nibbles). Selected portions of a word (fields) may be operated on while leaving the remainder of the word unchanged. Operations on fields longer than one nibble are performed serially with each successive nibble requiring an additional CPU cycle. For information regarding the full CPU instruction set see Section 5.3 INSTRUCTION SET.

#### 5.2.2 Registers

Figure 5.1 shows the programmers model of the CPU. A description of the register groups and their functions follows.

Figure 5.1. CPU Register Set

There are 198 nibbles of CPU resident RAM organized to provide four 64-bit working registers (A,B,C,D), five 64-bit scratch registers (R0,R1,R2,R3,R4), two 20-bit data pointer registers (D0,D1), an eight level hardware return stack (RSTK) for 20-bit addresses, and 16 bits of program status.

There are two types of registers on the CPU; those used for data and arithmetic operations, and those used for program and system control.

#### **ARITHMETIC/DATA REGISTERS:**

| A   | 64-bits | Working register - I/O register                  |

|-----|---------|--------------------------------------------------|

| B   | 64-bits | Working register                                 |

| C   | 64-bits | Working register - I/O register                  |

| D   | 64-bits | Working register                                 |

| R0  | 64-bits | Scratch register                                 |

| R1  | 64-bits | Scratch register                                 |

| R2  | 64-bits | Scratch register                                 |

| R3  | 64-bits | Scratch register                                 |

| R4  | 64-bits | Scratch register                                 |

| CRY | 1-bit   | Flag adjusted by arithmetic operations and tests |

#### CONTROL REGISTERS:

| P    | 4-bits  | Pointer register                   |

|------|---------|------------------------------------|

| DO   | 20-bits | Address pointer register           |

| D1   | 20-bits | Address pointer register           |

| PC   | 20-bits | Program Counter                    |

| RSTK | 20-bits | 8-level subroutine stack           |

| ST   | 16-bits | Program status flags               |

| HS   | 4-bits  | Hardware status flags              |

| OUT  | 12-bits | Keyscan/write only Output Register |

| IN   | 16-bits | Keyscan/read only Input Register   |

For the 1LT8 chip, only 10 bits of the OUT register and 10 bits of the IN register are used (including IR[15] (ON) and OR11 (BEEP)). When the unused bits of the OUT register are written to, nothing will happen external to the chip.

All arithmetic operations are performed using the 4 working registers: A, B, C, and D. Data transfers are performed principally with the A and C registers. The scratch registers are

Page 16

< HP CONFIDENTIAL >

A-1LT8-0601-1

used to temporarily hold the contents of the working registers.

#### 5.2.2.1 Field Selection

Subfields of the working registers may be manipulated using field selection. The possible field selections range from the entire register to any single nibble of the register. Certain subfields are designed for use in BCD calculations and others are designed for use in general data manipulation and data access. Nibble 0 is considered to be least significant by the ALU.

FIELD SELECTION FIELDS

| Р  | nibble pointed to by P register          |

|----|------------------------------------------|

| WP | nibble 0 through nibble pointed at by P  |

| XS | nibble 2 - Exponent sign                 |

| Х  | nibbles 0-2 - Exponent and exponent sign |

| S  | nibble 15 – Mantissa sign                |

| М  | nibbles 3-14 - Mantissa                  |

| В  | nibbles 0-1 - Exponent or byte field     |

| W  | nibbles 0-15 - Whole word                |

| А  | nibbles 0-4 – Address field              |

#### Nibbles of Register

# 15:14:13:12:11:10: 9: 8: 7: 6: 5: 4: 3: 2: 1: 0 |S| | |<---- A ----> |<---- W ----->|<-- X ->|

#### 5.2.2.2 Carry Bit

The Carry bit is adjusted when an arithmetic operation or test is performed. During a calculation, such as incrementing or decrementing a register, it is set if the calculation overflows or borrows and cleared if it does not. During a arithmetic test, such as comparing two registers for equality, it is set if the test is true and cleared if it is not.

#### 5.2.2.3 Pointer Registers

The CPU uses D0 and D1 to provide the source addresses for all

external data transfers. During execution of a data transfer instruction the local DPs of all peripheral chips are loaded with either D0 or D1. The data access will then occur utilizing the auto-increment feature of the local DPs. See SYSTEM BUS DESCRIPTION. It should be noted that D0 and D1 are merely registers and do not increment during data transfer.

The Pointer register is used in Field Selection operations with the working registers.

#### 5.2.2.4 **Program Counter and Return Stack**

The CPU resident PC is a true counter that increments in real time during instruction fetches. It can be accessed only using GOTO, GOSUB and RETURN instructions. Relative GOTOs and GOSUBs are handled using the ALU to modify the PC. Absolute GOTOs and GOSUBs are handled using a parallel load feature. All non-increment modifications to the PC are eventually followed by a load to the local PCs on all peripheral chips.

The subroutine return stack consists of eight 20-bit registers implemented as a LIFO. Subroutine call and return instructions automatically push and pop addresses on this stack. If a ninth address is pushed onto the stack, the oldest address will be lost and will be replaced by zero if it is eventually popped from the stack. This feature insures that repeated returns will eventually end at address zero. The return stack can also be manipulated through use of the push (RSTK=C) and pop (C=RSTK) instructions.

#### 5.2.2.5 Status Bits

Additional program control is provided by the 16-bit Program Status register and the 4-bit Hardware Status register. Each Program status bit can be individually set, reset, and tested. The upper four bits may only be accessed individually. The lower 12 Program status bits may be collectively manipulated as the ST register.

The four Hardware Status bits are set (but not cleared) by hardware related events, and must therefore be cleared beforehand in order to detect a particular occurrence. They are individually accessible by name. The Module Pulled bit (MP) is set when the NINTX line is pulled low (regardless of whether an interrupt is actually executed). The Sticky Bit (SB) is set when a non-zero bit or digit shifts off the right end of a working register as the result of a shift right instruction, or the least significant nibble of a working register is non-zero prior to a shift right circular instruction. The Service Request (SR) bit is set as a result of a response to the SREQ? instruction. The external

Page 18

< HP CONFIDENTIAL >

Module Missing bit (XM) is set by execution of a "00" opcode (RTNSXM instruction). Since the BUS[0:3] is precharged low, the CPU will receive a RTNSXM instruction if no device responds to a PC READ bus command.

HARDWARE STATUS: 4 bits

| Bit | Symbol | Name                    |

|-----|--------|-------------------------|

|     |        |                         |

| 3   | MP     | Module Pulled           |

| 2   | SR     | Service Request         |

| 1   | SB     | Sticky Bit              |

| 0   | XM     | External Module Missing |

#### 5.2.3 Loading Data from Memory

When data is read from an external device into a register, the CPU places the lowest addressed nibble in the least significant nibble of the selected field in the register. For example, if the data shown below in memory is read into the C register using the **C=DAT1** 4 instruction, the data in the register will be arranged as shown:

| Memory<br>Location | Value |   | L           |   | с |   | Reg | ist | cer | 2 |   |  |   |   |

|--------------------|-------|---|-------------|---|---|---|-----|-----|-----|---|---|--|---|---|

| 1000<br>1001       | 0     | _ | <br>   <br> |   |   |   | 3   |     | 2   |   | 1 |  | 0 |   |

| 1002<br>1003       | 2     |   | 15          | • | • | • | 3   |     | 2   |   | 1 |  | 0 | • |

| •                  | -     |   |             |   |   |   |     |     |     |   |   |  |   |   |

| •                  |       |   |             |   |   |   |     |     |     |   |   |  |   |   |

This principle also applies to loading constants into a CPU register such as C, D0, or D1, since the CPU must read the constant from the instruction opcode in memory. For example, the instruction LCHEX 3210 produces the opcode 330123 and the C register is loaded as shown above (assuming P=0).

#### 5.2.4 Storing Data in Memory

When data is written from a register to an external device, the CPU places the least significant nibble of the register in the first addressed nibble of the memory location. For example, if the data shown above in the C register is written to memory using the DAT1=C 4 instruction, the data will be written to memory as shown.

#### 5.2.5 HEX/DEC Modes

All arithmetic operations, except for those listed below, are performed according to the HEX or DEC mode setting. The mode is set using the SETHEX or SETDEC instruction. The following operations are performed in HEX regardless of the mode setting.

| C+P+1        |              |

|--------------|--------------|

| D0=D0+ n     | D0=D0- n     |

| D1=D1+ n     | D1=D1- n     |

| P=P+1        | P=P-1        |

| A=A+CON fs,N | A=A-CON fs,N |

| B=B+CON fs,N | B=B-CON fs,N |

| C=C+CON fs,N | C=C-CON fs,N |

| D=D+CON fs,N | D=D-CON fs,N |

#### 5.3 INSTRUCTION SET

#### 5.3.1 General Information

Many CPU instructions modify only a selected field of a register. Nibbles not explicitly changed by an instruction are left unchanged.

The offset addresses for the relative jump and gosub instructions are in two's compliment form with the least significant nibble first. Offsets for jump instructions are relative to the least significant nibble of the offset. Offsets for gosub instructions are relative to the first nibble of the next instruction.

Conditional instructions have two cycle counts listed. The second (and smaller count) is if the condition (test) is false.

#### 5.3.1.1 Glossary of Symbols

DATn Memory location addressed by either D0 or D1.

- fs Field selection specifier.

- D Number of nibbles operated upon. Used in calculation of cycle counts.

# 5.3.2 Instruction Description

| MNEMON | CODE | сүс | FLG                                           | DESCRIPTION                                          |

|--------|------|-----|-----------------------------------------------|------------------------------------------------------|

| RTNSXM | 00   | 9   | HS0                                           | Return and set HS0                                   |

| RTN    | 01   | 9   |                                               | Return from subroutine                               |

| RTNSC  | 02   | 9   | CRY                                           | Return and set CRY                                   |

| RTNCC  | 03   | 9   | CRY                                           | Return and clear CRY                                 |

| SETHEX | 04   | 3   |                                               | Set ALU to HEX mode                                  |

| SETDEC | 05   | 3   |                                               | Set ALU to BCD mode                                  |

| RSTK=C | 06   | 8   |                                               | Push C(A) onto stack                                 |

| C=RSTK | 07   | 8   |                                               | Pop stack to C(A)                                    |

| CLRST  | 08   | 5   | ST                                            | Clear ST[0:11]                                       |

| C=ST   | 09   | 5   |                                               | Load C(X) with ST[0:11]                              |

| ST=C   | 0A   | 5   | ST                                            | Load ST[0:11] with C(X)                              |

| CSTEX  | 0B   | 5   | ST                                            | Exchange ST[0:11] with C(X)                          |

| P=P+1  | 0C   | 3   | CRY                                           | Hexadecimal increment of P. F wraps to O.            |

| P=P-1  | 0D   | 3   | CRY                                           | Hexadecimal decrement of P. 0 wraps to F.            |

|        |      |     |                                               | Logical AND<br>Logical OR                            |

|        |      |     | f:32                                          | LO fs t: HEX t: HEX                                  |

|        |      |     | X00<br>X00<br>X00<br>X10<br>X10<br>X11<br>011 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

Page 22

< HP CONFIDENTIAL >

| MNEMON              | CODE                     | CYC             | FLG  | DESCRIPTION                                                                                                                                                                                                                                                                                                    |

|---------------------|--------------------------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTI                 | OF                       | 9               |      | Return from interrupt and enable interrupt handling.                                                                                                                                                                                                                                                           |

| ss=r                | 10s                      | 19              |      | Copy A or C to scratch register.                                                                                                                                                                                                                                                                               |

| r=ss                | 11s                      | 19              |      | Copy scratch register to A or C.                                                                                                                                                                                                                                                                               |

| rssEX               | 12s                      | 19              |      | Exchange A or C with scratch register.                                                                                                                                                                                                                                                                         |

|                     |                          |                 | -    | X000 scratch register R0<br>X001 scratch register R1<br>X010 scratch register R1<br>X010 scratch register R2<br>X011 scratch register R3<br>X100 scratch register R4<br>X101 scratch register R1<br>X110 scratch register R2<br>X111 scratch register R3<br>OXXX working register A<br>1XXX working register C |

|                     |                          |                 |      |                                                                                                                                                                                                                                                                                                                |

| MNEMON              | CODE                     | СҮС             | FLG  | DESCRIPTION                                                                                                                                                                                                                                                                                                    |

| MNEMON<br><br>d=r   | CODE<br>13t              |                 |      | DESCRIPTION<br>Copy A field of A or C to D0 or D1                                                                                                                                                                                                                                                              |

|                     |                          | 8               |      |                                                                                                                                                                                                                                                                                                                |

| <br>d=r             | <br>13t                  | 8<br>7          |      | Copy A field of A or C to D0 or D1<br>Copy nibbles 0-3 of A or C to nib. 0-3 of D0                                                                                                                                                                                                                             |

| d=r<br>d=rs         | <br>13t<br>13t           | <br>8<br>7<br>8 | <br> | Copy A field of A or C to D0 or D1<br>Copy nibbles 0-3 of A or C to nib. 0-3 of D0<br>or D1                                                                                                                                                                                                                    |

| d=r<br>d=rs<br>rdEX | 13t<br>13t<br>13t<br>13t | <br>8<br>7<br>8 | <br> | Copy A field of A or C to D0 or D1<br>Copy nibbles 0-3 of A or C to nib. 0-3 of D0<br>or D1<br>Exchange A field of A or C r<-dwith D0 or D1<br>Exchange nibbles 0-3 of A r<-d or C with nib.                                                                                                                   |

A-1LT8-0601-1 < HP CONFIDENTIAL >

| MNEMON |   | CODE | CYC           | FLG | DESCRIPTION                                                   |

|--------|---|------|---------------|-----|---------------------------------------------------------------|

| DATn=r | A | 14t  | <b></b><br>17 |     | Write A field of A or C to location addressed<br>by D0 or D1. |

| DATn=r | B | 14t  | 14            |     | Write B field of A or C to location addressed by D0 or D1.    |

| r=DATn | A | 14t  | 18            |     | Read A field of A or C from location addressed by D0 or D1.   |

| r=DATn | B | 14t  | 15            |     | Read B field of A or C from location addressed by D0 or D1.   |

|        |   |      | t: H          | IEX | t: HEX                                                        |

|        |   |      |               |     |                                                               |

|        |   |      |               | 0   | DATO=A A 8 DATO=A B                                           |

|        |   |      |               | 1   | DAT1=A A 9 DAT1=A B                                           |

|        |   |      |               | 2   | A=DATO A A A=DATO B                                           |

|        |   |      |               | 3   | A=DAT1 A B A=DAT1 B                                           |

|        |   |      |               | 4   | DATO=C A C DATO=C B                                           |

|        |   |      |               | 5   | DAT1=C A D DAT1=C B                                           |

|        |   |      |               | 6   | C=DATO A E C=DATO B                                           |

|        |   |      |               | 7   | C=DAT1 A F C=DAT1 B                                           |

| MNEMON   |    | CODE     | CYC          | FLG      | DESCRIPTION                                                        |

|----------|----|----------|--------------|----------|--------------------------------------------------------------------|

| DATn=r 1 | fs | 15tn     | 16+D         |          | Write selected field of A or C to location addressed by D0 or D1.  |

| DATn=r 1 | N  | 15t(N-1) | 16+N         |          | Write nib. 0-(N-1) of A or C to location<br>addressed by D0 or D1. |

| r=DATn 1 | fs | 15tn     | 17+D         |          | Read selected field of A or C from location addressed by D0 or D1. |

| r=DATn 1 | N  | 15t(N-1) | 17+N         |          | Read nib. 0-(N-1) of A or C to location addressed by D0 or D1.     |

|          |    | t        | : 3210       | )        | n: 3210                                                            |

|          |    |          | <br>X000     | -<br>D 1 | <br>DATO=A X000 P                                                  |

|          |    |          | X002         |          | DAT1=A X001 WP                                                     |

|          |    |          | X010         |          | A=DATO X010 XS                                                     |

|          |    |          | X011         | l i      | A=DAT1 X011 X                                                      |

|          |    |          | X100         |          | DATO=C X100 S                                                      |

|          |    |          | X101         |          | DAT1=C X101 M                                                      |

|          |    |          |              |          | C=DATO X110 B                                                      |

|          |    |          | X113         | 1 (      | C=DAT1 X111 W                                                      |

|          |    |          | 0XXX<br>1XXX |          | fs specified by n<br>nibbles 0-N                                   |

| MNEMON      | CODE    | сүс     | FLG | DESCRIPTION                                                                                                                                            |

|-------------|---------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0=D0+ n    | 16n     | 7       | CRY | Hex increment of D0 by n+1. F wraps to 0.                                                                                                              |

| D1=D1+ n    | 17n     | 7       | CRY | Hex increment of D1 by n+1. F wraps to 0.                                                                                                              |

| D0=D0- n    | 18n     | 7       | CRY | Hex decrement of D0 by n+1. 0 wraps to F.                                                                                                              |

| D0= nn      | 19nn    | 4       |     | Load B field of D0 with nn.                                                                                                                            |

| D0= nnnn    | 1Annnn  | 6       |     | Load nib. 0-3 of D0 with nnnn.                                                                                                                         |

| D0= nnnnn   | 1Bnnnnn | 7       |     | Load D0 with nnnnn.                                                                                                                                    |

| D1=D1- n    | 1Cn     | 7       | CRY | Hex decrement of D1 by n+1. 0 wraps to F.                                                                                                              |

| D1= nn      | 1Dnn    | 4       |     | Load B field of D1 with nn.                                                                                                                            |

| D1= nnnn    | lEnnnn  | 6       |     | Load nib. 0-3 of D1 with nnnn.                                                                                                                         |

| D1= nnnnn   | lFnnnnn | 7       |     | Load D1 with nnnnn.                                                                                                                                    |

| P= n        | 2n      | 2       |     | Load pointer with n.                                                                                                                                   |

| LC nnn      | 3tnnn   | 3+t     |     | Load C with t+1 nibbles nnn beginning at<br>the pointer position with wrap around<br>capability. This mnemonic is not supported<br>by most assemblers. |

| LCHEX n.n   | Same.   | 3+t     |     | These mnemonics are supported by most<br>assemblers                                                                                                    |

| LC(i) nnnnn | Same.   | 3+t     |     | Same.                                                                                                                                                  |

| LCASC 'c.c' | Same.   | 3+t     |     | Same.                                                                                                                                                  |

| RTNC        | 400     | 10<br>3 |     | Return if CRY is set.                                                                                                                                  |

| GOC         | 4aa     | 10<br>3 |     | Jump relative if CRY is set.                                                                                                                           |

| RTNNC       | 500     | 10<br>3 |     | Return if CRY is clear.                                                                                                                                |

| GONC        | 5aa     | 10<br>3 |     | Jump relative if CRY is clear.                                                                                                                         |

< HP CONFIDENTIAL >

A-1LT8-0601-1

| MNEMON      | CODE    | CYC | FLG | DESCRIPTION                                                                                                                           |

|-------------|---------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| бото        | 6aaa    | 11  |     | Relative jump.                                                                                                                        |

| GOSUB       | 7aaa    | 12  |     | Relative gosub.                                                                                                                       |

| OUT=CS      | 800     | 4   |     | Load nib. 0 of OR with nib. 0 of C.                                                                                                   |

| OUT=C       | 801     | 6   |     | Load OR with X field of C.                                                                                                            |

| A=IN        | 802     | 7   |     | Load nib. 0-3 of A from IR.                                                                                                           |

| C=IN        | 803     | 7   |     | Load nib. 0-3 of C from IR.                                                                                                           |

| UNCNFG      | 804     | 12  |     | Unconfigure a configured device addressed by<br>A field of C.                                                                         |

| CONFIG      | 805     | 11  |     | Configure an unconfigured device that has DAISYIN=1 at the address in A field of C.                                                   |

| C=ID        | 806     | 11  |     | Load the A field of C with the ID of an unconfigured device that has DAISYIN=1.                                                       |

| SHUTDN      | 807     | 6   |     | CPU issues the NOP bus command to eliminate<br>all memory ops then issues the SHUTDOWN bus<br>command and enters the low power state. |

| INTON       | 8080    | 5   |     | Unmask maskable IR interrupts.                                                                                                        |

| RSI         | 80810   | 6   |     | Causes any IR line high to be considered a<br>new interrupt regardless of whether all IR<br>lines have returned low.                  |

| LAHEX n.n   | 8082tn. | 6+t |     | Load A with t+1 nibbles nnn beginning at<br>the pointer position with wrap around<br>capability.                                      |

| LA(i) nnnnn | Same.   | 6+t |     | Same.                                                                                                                                 |

| LAASC 'c.c' | Same.   | 6+t |     | Same.                                                                                                                                 |

| BUSCB       | 8083    | 7   |     | Issue the BUSCB bus command.                                                                                                          |

CODE CYC FLG DESCRIPTION MNEMON \_\_\_\_\_ \_\_\_ \_\_\_ \_\_\_\_ ABIT=0 n --- Clear specified bit (0 to F) of A register. 8084n 6 --- Set specified bit (0 to F) of A register. ABIT=1 n 8085n 6 **?ABIT=0 n** 8086n00 16 CRY Return and set CRY if specified bit (0 to F) RTNYES 9 of A register is 0. CRY Jump relative and set CRY if specified bit (0 **?ABIT=0 n** 8086naa 16 GOYES 9 to F) of A register is 0. **?ABIT=1 n** 8087n00 16 CRY Return and set CRY if specified bit (0 to F) RTNYES 9 of A register is 1. CRY Jump relative and set CRY if specified bit (0 **?ABIT=1 n** 8087naa 16 GOYES 9 to F) of A register is 1. CBIT=0 n --- Clear specified bit (0 to F) of C register. 8088n 6 --- Set specified bit (0 to F) of C register. CBIT=1 n 8089n 6 CRY Return and set CRY if specified bit (0 to F) **?CBIT=0 n** 808An00 16 of C register is 0. RTNYES 9 CRY Jump relative and set CRY if specified bit (0 **?CBIT=0 n** 808Anaa 16 to F) of C register is 0. GOYES 9 CRY Return and set CRY if specified bit (0 to F) **?CBIT=1 n** 808Bn00 16 of C register is 1. RTNYES 9 CRY Jump relative and set CRY if specified bit (0 **?CBIT=1 n** 808Bnaa 16 to F) of C register is 1. GOYES 9

A-1LT8-0601-1

MNEMON CODE CYC FLG DESCRIPTION

- PC=(A) 808C 23 --- Indirect Jump. Data addressed by the A field of the A register is placed in the PC and execution resumes there.

- BUSCD 808D 7 --- Issue the BUSCD bus command.

- PC=(C) 808E 23 --- Indirect Jump. Data addressed by the A field of the C register is placed in the PC and execution resumes there.

- **INTOFF** 808F 5 --- Mask the maskable IR interrupts.

- C+P+1 809 8 CRY Hex increment of A field of C by P+1. Wraps to 0.

- **RESET** 80A 6 --- Issue the RESET bus command. All chips perform a local reset.

- BUSCC 80B 6 --- Issue the BUSCC bus command. The device addressed by its DP performs a specialized function.

- C=P n 80Cn 6 --- Load nibble n of C with P.

P=C n 80Dn 6 --- Load P with nibble n of C.

- SREQ? 80E 7 HS2 Issue POLL bus command and latch system bus into nib 0 of C. HS2 is set if this nibble is not zero.

- **CPEX n** 80Fn 6 --- Exchange the pointer with nibble n of C.

| MNEMON | CODE | CYC | FLG | DESCRIPTION                                                                                                             |  |  |  |  |

|--------|------|-----|-----|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| rSLC   | 81s  | 21  |     | Left circular nibble shift of entire 16<br>nibble register.                                                             |  |  |  |  |

| rSRC   | 81s  | 21  | HS1 | Right circular nibble shift of entire 16<br>nibble register. Sticky bit is set if a non-<br>zero nibble is shifted off. |  |  |  |  |

| rSRB   | 81s  | 20  | HS1 | Right bit shift of entire 64 bit register.<br>Sticky bit is set if a non-zero bit is<br>shifted off.<br>s:3210          |  |  |  |  |

|        |      |     |     | XX00 A register.<br>XX01 B register.<br>XX10 C register.<br>XX11 D register.<br>00XX rSLC<br>01XX rSRC<br>11XX rSRB     |  |  |  |  |

MNEMON CODE CYC FLG DESCRIPTION -----\_\_\_\_\_ **r=r+CON fs,n** 818frn 5+D CRY Hex increment of register r by n+1. r=r-CON fs,n 818frn 5+D CRY Hex decrement of register r by n+1.

| f: 3210 |   | r: 3210 |             |

|---------|---|---------|-------------|

|         |   |         |             |

|         |   | XX00    | A register  |

| X011    | Х | XX01    | B register  |

| X101    | М | XX10    | C register  |

| X110    | В | XX11    | D register  |

| 0111    | W | OXXX    | addition    |

| 1111    | Α | 1XXX    | subtraction |

MNEMON CODE CYC FLG DESCRIPTION **rSRB.F fs** 819fr 6+D HS1 Right bit shift of register field. Sticky bit is set if a non-zero bit is shifted off.

| f: 3210 |    | r: 3210 |            |

|---------|----|---------|------------|

|         |    |         |            |

| X000    | Р  | XX00    | A register |

| X001    | WP | XX01    | B register |

| X010    | XS | XX10    | C register |

| X011    | Х  | XX11    | D register |

| X100    | S  |         |            |

| X101    | М  |         |            |

| X110    | В  |         |            |

| 0111    | W  |         |            |

| 1111    | Α  |         |            |

|         |    |         |            |

| MNEMON     | CODE   | CYC FI | LG DESCRIPTION                                      |        |

|------------|--------|--------|-----------------------------------------------------|--------|

| ss=r.F fs  | 81Afrn | 6+D    | Copy selected field of A or C to s register.        | cratch |

| r=ss.F fs  | 81Afrn | 6+D    | Copy selected field of scratch register<br>or C.    | to A   |

| rssEX.F fs | 81Afrn | 6+D    | Exchange selected field of A or C scratch register. | with   |

|            | f:3210 |        | r: 3210 n: HEX                                      |        |

|            | X000   | Р      | 0000 ss=r X000 R0                                   |        |

|            | X001   | WP     | 0001 r=ss X001 R1                                   |        |

|            | X010   | XS     | 0010 rssEX X010 R2                                  |        |

|            | X011   | Х      | X011 R3                                             |        |

|            | X100   | S      | X100 R4                                             |        |

|            | X101   | М      | X101 R1                                             |        |

|            | X110   | В      | X110 R2                                             |        |

|            | 0111   | W      | X111 R3                                             |        |

|            | 1111   | Α      | OXXX A                                              |        |

|            |        |        | 1XXX C                                              |        |

| MNEMON |       | CODE  | CYC | FLG    | DESCRIPTION                                                                   |    |

|--------|-------|-------|-----|--------|-------------------------------------------------------------------------------|----|

| PC=A   |       | 81B2  | 16  |        | Absolute jump to the address contained in the A field of the A register.      | he |

| PC=C   |       | 81B3  | 16  |        | Absolute jump to the address contained in the A field of the C register.      | he |

| A=PC   |       | 81B4  | 9   |        | Move the address of the next instruction the A field of the A register.       | to |

| C=PC   |       | 81B5  | 9   |        | Move the address of the next instruction the A field of the C register.       | to |

| APCEX  |       | 81B6  | 16  |        | Exchange the A field of A and the current (pointing to the next instruction). | PC |

| CPCEX  |       | 81B7  | 16  |        | Exchange the A field of C and the current (pointing to the next instruction). | PC |

| CLRHSN | n     | 82n   | 3   | HSn    | Clear the hardware status flags specified the bitmap of n.                    | by |

| XM=0   |       | 821   | 3   | HS0    | •                                                                             |    |

| SB=0   |       | 822   | 3   | HS1    |                                                                               |    |

| SR=0   |       | 824   | 3   | HS2    |                                                                               |    |

| MP=0   |       | 828   | 3   | HS3    |                                                                               |    |

| CLRHST |       | 82F   | 3   | HS0-3  |                                                                               |    |

|        | n<br> | :3210 |     |        |                                                                               |    |

|        |       | XXX1  |     | Missin | g module; set by RTNSXM                                                       |    |

| XXXI | MISSING MODULE; SEC DY RINSAM             |  |

|------|-------------------------------------------|--|

| XX1X | Sticky bit; set by rotate and shift right |  |

| X1XX | Service request response                  |  |

|      |                                           |  |

| 1XXX | Module | interrupt | line | (*INT) | pulled | low |

|------|--------|-----------|------|--------|--------|-----|

|------|--------|-----------|------|--------|--------|-----|