# Microbaud Developments

MACHINE LANGUAGE INTERFACE Dear Customer,

Unfortunately we have discovered three errors in the Construction Guide of which you should be aware. Please emend your copy as follows:-

The fourth paragraph below "CONSTRUCTION" should be changed to read:—

bend pins 9 to 17 (EXCEPT PIN 12) out herizontal on both RAMs. Now take .......

The second paragraph below the heading "EPROM CURPENT DRAIN" contains two mistakes. It should read as follows:--

\* This must be done prior to the insertion of the IC - it can still be out if the rest of the EPROM CURRENT DPAIN modification is not carried out at this stage.

Good luck with the construction of your MLI, and we wish you every success with your future machine gode programming.

Yours sincerely,

rivall lager

for MICROBAUD DEVELOPMENTS.

## DISCLAIMER

Whilst every effort has been made to ensure that this Machine Language Interface will operate as indicated efficiently and properly if constructed according to the attached details, or purchased assembled, no responsibility will be accepted in respect of failure for any reason at all of the aforesaid Interface to operate effectively or at all due to any fault in design or otherwise and no responsibility is accepted for any damage caused by the Interface to any connected equipment. Further, no responsibility is accepted in respect of any injury or damage of any kind caused by any fault in the design, construction or otherwise of the Interface as aforesaid.

### SEMICONDUCTORS

- 2 CD4011 Quad 2-input NAND (U14,U27)

- CD4012 Dual 4-input NAND (U22)

- 2 CD4013 Dual D Flip-Flop (U1, U13)

- 2 CD4017 Decoded Decimal Counter (UZ, U3)

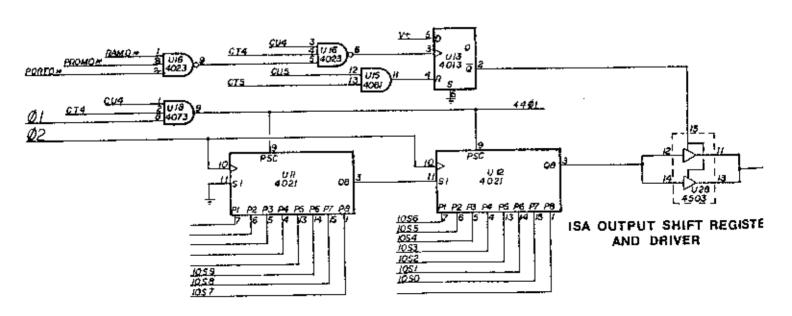

- 2 CD4021 8-stage Parallel Input Shift Register (U11, U12)

- 2 CD4023 Triple 3-input NAND (U16, U17)

- 2 CD4028 BCD to Decimal Decoder (U25, U26)

- CD4049 Hex Inverter (U32)

- CD4052 Differential 4-channel Multiplexer (US)

- CD4068 8-input AND (U21) ?

- 1 CD4073 Triple 3-input AND (U18)

- 1 CD4078 8 input NOR (U20)

- 2 CD4081 Quad 2-input AND (U15, U19)

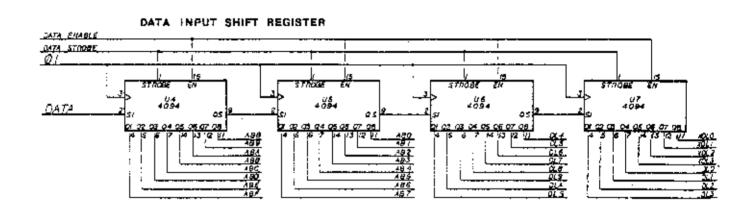

- 6 CD4094 8-bit Shift and Store Register (U4, U5, U6, U7, U9, U10)

- 1 CD4503 (or 40097) 3-state Hex Buffer (U28)

- 2 MM74C85 (or 40085) 4-bit Magnitude Comparator (U23, U24)

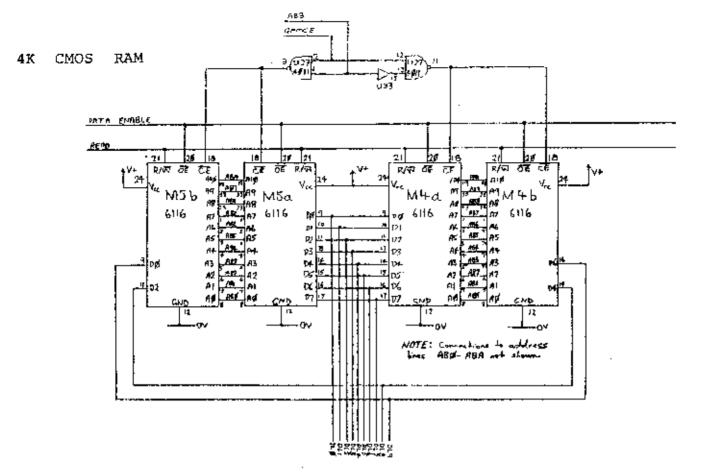

- 4 6116 4XX4 CHOS RAH (M4a, M4b, MSa, M5b)

- These need to be pre-programmed with at least 1 2716 2KOS EPRON (M2)

- the WROM instruction. A suitable set is available 1 2732 4Kx8 EPROM (143) from Microbaud Developments.

- 1 2N3906 transistor

- 1 Miniature red LED

- 1 1N4G02 rectifier diode

#### CAPACITORS

- 1 100uF/16VW axial electrolytic 9 0.1uF bypass capacitors ("redcaps")

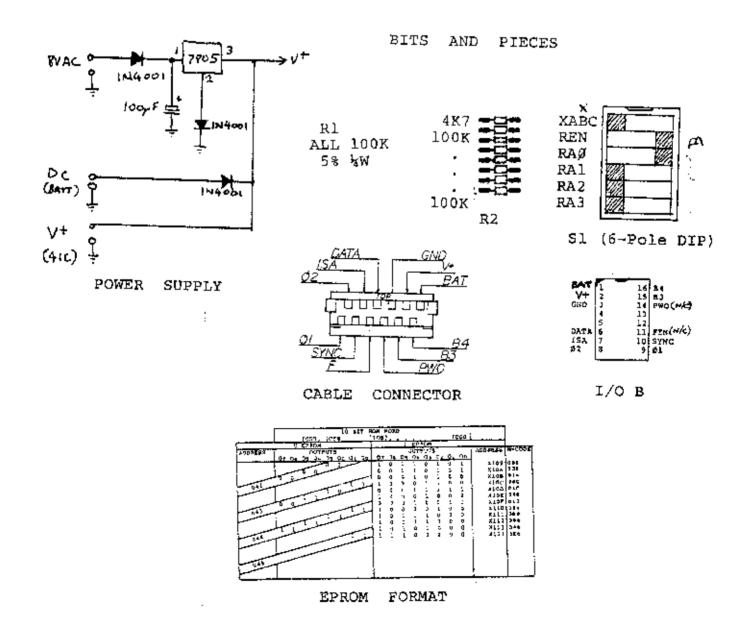

## RESISTORS (1/4W, 5%)

- 13 100K

- 1 4K7

## MYSCETTANEOUS

Solder, spacers, nuts, bolts, etc.

## OPTIONAL AC POWER SUPPLY

- 1 7805 regulator

- 2 0.1uF bypass capacitors ("redcaps")

- 2 th4002 rectifier diodes

- 1 100uF/16VW axial electrolytic

## CONSTRUCTION

percent 4 Propagation and tage

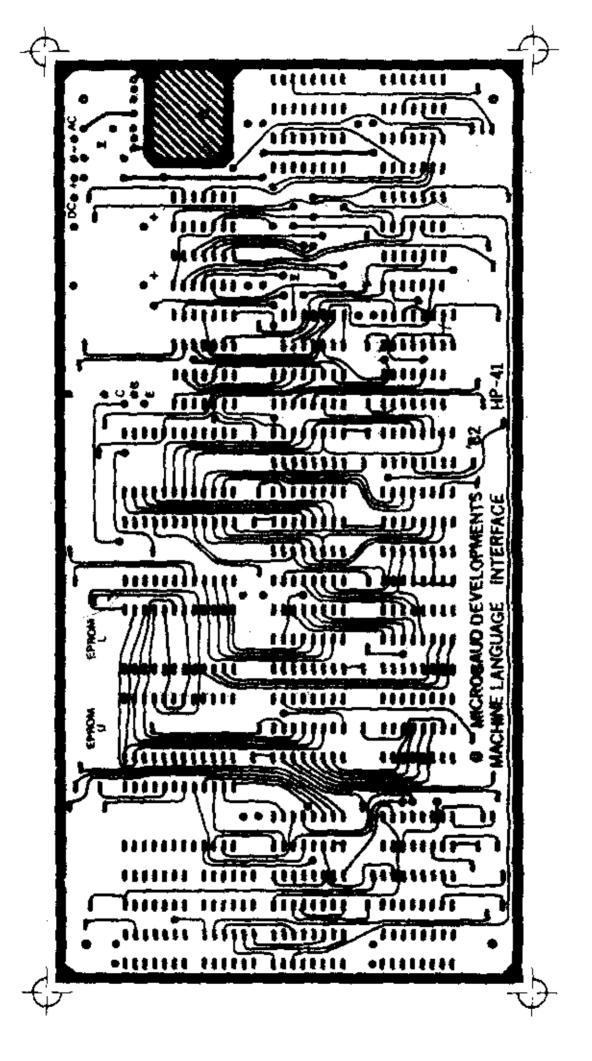

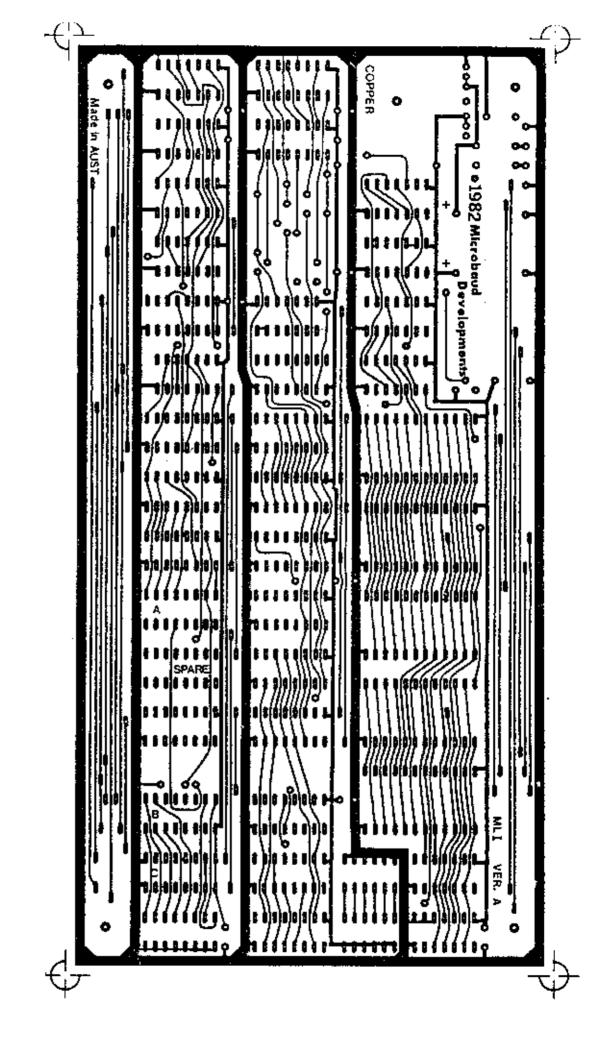

The first task is to drill the four mounting holes on the PCB, and, if you intend using the optional AC Power Supply, drill the mounting hole for the regulator. Next, fix the 16 pin DTP plug onto one gnd of the ribbon cable (this is done using a special clamping tool or a hammer[!!]). Solder the other end of the cable to the connector of an old module, having first removed and discarded the module PCB. Ensure that pin 1 goes to V+, pin 16 to 84 etc. This lead is crucial to the whole MTLI, so it would be best to triple check the lead for continuity and accuracy.

Start construction on the PCB by placing the resistors and diodes into position. Check the orientation of the diodes and solder these components into the board. Next solder in the IC sockets, noting that no sockets are required for M1, I/O A, I/O C and 'SPARE', and the 6 pole DIP switch. If you are not using sockets be sure the ICs are correctly oriented, and solder the power supply pins first, with the barrel of the soldering iron connected to the ground track of the PCB. N.B. DO NOT solder in the CMOS RAMs yet! place the capacitors, transistor and LED into the board, once again checking the orientation, and solder these and the battery clip to the board.

## INTRODUCTION

The Microbaud Developments Machine Language Interface has two major sections. Firstly, it provides up to 4K of EPROK which can hold routines dedicated to the MLI and routines which are frequently used and are best kept in a permanent form, such as CODE, DECODE, an assembler and disassembler.

Secondly, the MLI contains 4K of CHOS RAW which is totally independent of the calculator's main memory and is under your total control. This memory is treated as an applications ROW by the calculator, and it is in this area that you may write your own machine language fuctions and routines.

There is also provision in the MLI for an external set of input/output ports, although these are not fully implemented on the board.

## TECHNICAL OVERVIEW

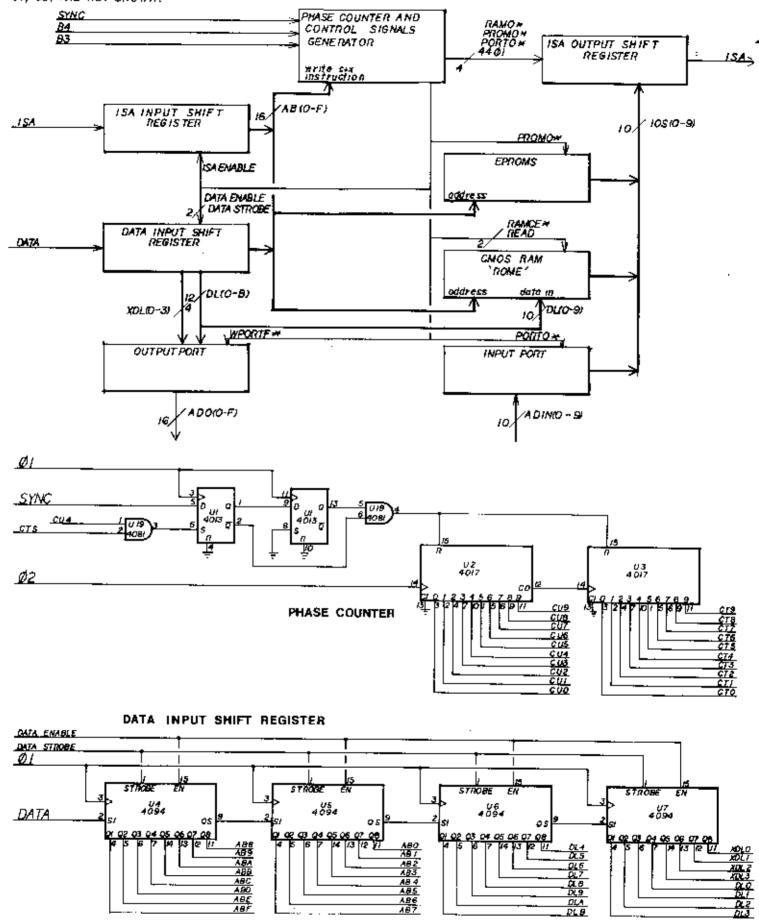

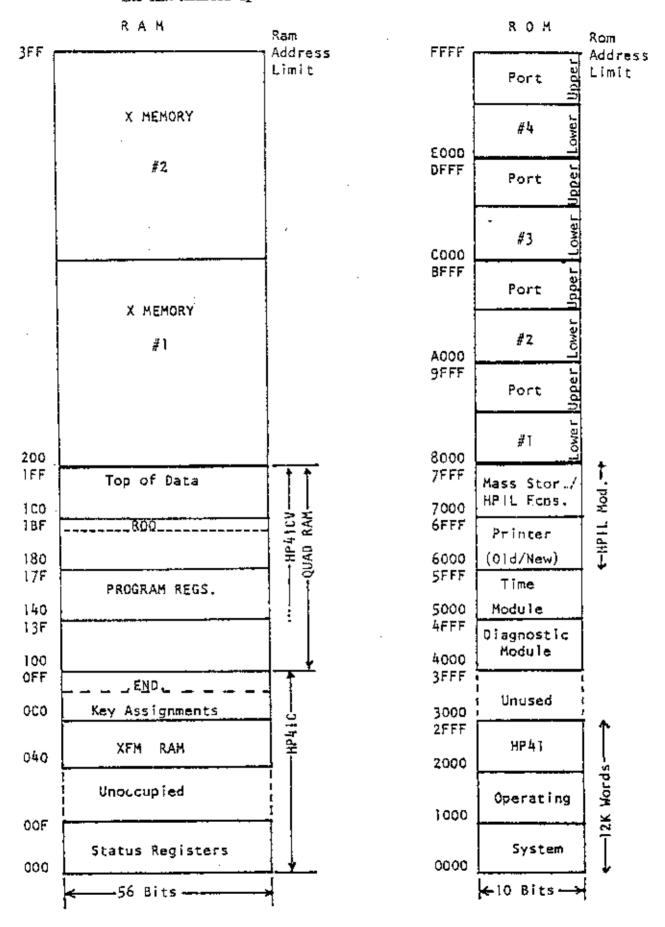

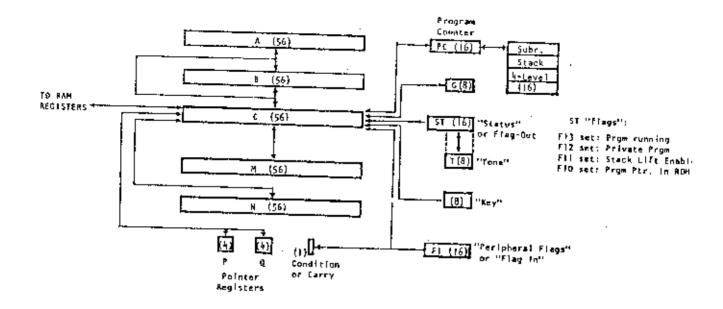

The HP-41C/CV uses ten bit words to communicate data and instructions in a serial format both internally and with external devices such as applications ROAs or the MLI. On the block diagram you can see that data shifted out on the ISA line from the MLI to the HP-41 may come from the EPROM or the CNOS RAM (or the Input port if it is implemented). One of these sources is selected by the Address Bus lines AB(C-F).

During any given 56-bit HP-41 machine cycle, sixteen bits of ROH address information is shifted out through the ISA line. They arrive at the MLI ISA Input Shift Register which latches them. ISA Enable (from the Control Signals Generator) gates this address onto the Address Bus. At this stage comparators check to see if the address on the Eus matches either the EPROM address or the RAM address. If either of these addresses match, the appropriate control signals (e.g. RAMO\*, PORTO\*, PROMO\*) are asserted and the ISA Output Shift Register has the ten bit word on IOS(0-9) dumped into it at the correct time, and this word is subsequently shifted out.

The NLI decodes a special instriction in order to write to the CHOS RAM. The instruction is WROM (or WRITE SAM), hex code 040, and is a MOP in the MP-41 so that it does not affect the subsequent 56-bit machine cycle. When the write has been decoded, the data bits are used to determine the Note that the Data Input Shift Register latches the 'C' register in the HP-41 CPU (not the user-level 'c' register) whenever the least significant bit of C becomes DLD, thus the ten bit word loaded into RAM is the lowest ten bits of the C register.

Each instruction which arrives at the MLI is first latched into the ISA Input Shift Register, and then goes to the Control Signals Generator via the Address Bus AB(6-F). The WROM instruction is decoded in the Control Signals Generator and the most significant bits of the Data Input Shift Register are placed in the Address Bus AB(0-F), while the Data Lines BL(C-9) are gated to the PAN inputs. When both READ and RANCE\* are low (i.e. READ is not asserted and RANCE\* is asserted), the ten bit word on the Data Line DL(D-9) is written into the RAM.

## PARTS LIST

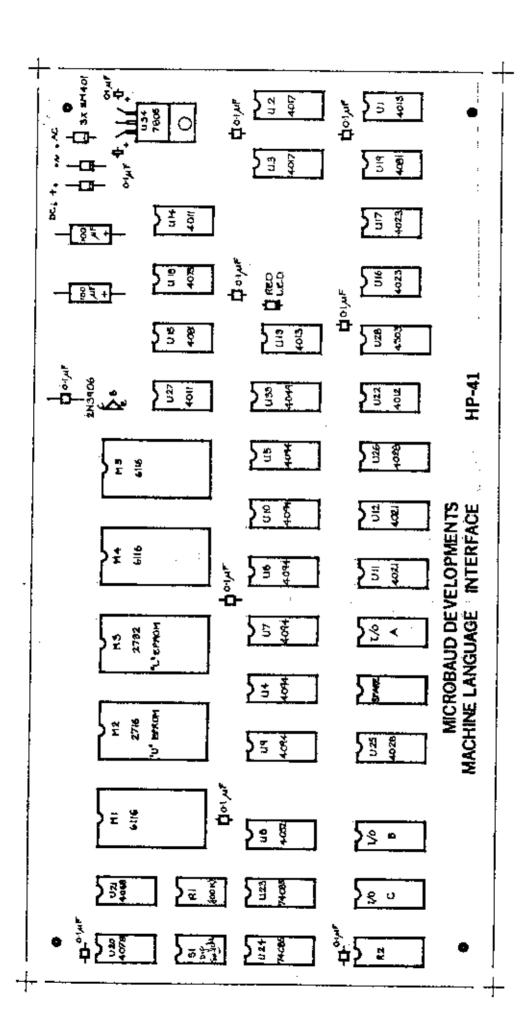

- 1 PCB "Microbaud Developments Macine Language Interface", 245x125mm

- 1 case, 250x145x30mm, e.g. custom-built marviplate steel box available from Microbaud Developments

- 1 16 pin DIL plug

- 1 6 pole DIP switch

- 1 battery holder (AXAA NiCd or 3xAA Alkaline)

- 1 battery clip (to suit battery holder)

- 1 length 16 core ribbon cable, about 35cm

- 1 old HP module

## SOCKETS (if required)

- 4 24 pin DIL

- 18 16 pin DIL (note that at least 2 24 pin and

- 12 14 pin DIL 1 16 pin socket is required)

At this stage it is good practice to visually check your soldering, cleaning away blobs and strands of solder which may short tracks. Once the board has been cleaned and checked, all the ICs except the CMOS RAMs may be plugged into their sockets. Ensuring that a suitable set of EPROMS has been plugged into the board, disable the RAM by switching the RAM Enable switch (AND the XABC switch) to 'off', plug the ribbon cable into I/O B and a calculator and press 'ON'. Execute a CAT 2 and you should see the EPROM functions displayed. Try assigning 'CODE' to a key. Place the following string into ALPHA: "10414243444546". XBQ "CODE" (or press your assigned key. If "ABCDEF" appears in the X-register everything is fine.

The next step is to solder a piece of thin wire (wire wrap wire is recommended) between pin 15 of I/O C and the hole at the top right of the 'I/ EPROM. Now comes the tricky part! We have four RAMs which we will call M4a, M4b, M5a and M5b. It may be best to tag the RAMs so that you don't get too confused in the following section. Take M4b and M5b and bend pins 9 to 17 out horizontal on both RAMs. Now take M4b and carefully bend pins 9, 10, 11, 13, 15 and 17 right up out of the way. Do the same to pins 10, 13, 14, 15, 16 and 17 of M5b. Place M4b on top of M4a piggy-back style and solder the remaining unbent pins of M4b to the corresponding pins directly below on CM4a. Give M5a and M5b the same treatment. Now plug the M4 and M5 RAM sets into their appropriate sockets (or solder them into the board).

pin 16 of M4b should be overlapping pin 9 of M5b, as should pin 14 of M4b with pin 11 of M5b. Solder these two sets of overlapping pins so that there are two 'bridges' between the two RAM sets. Solder a piece of wire to each 'bridge' and connect one to each of the two adjacent holes on the right side of I/O B. The order in which they are connected is not important.

Switch the RAM Address switches to 8000, that is RAM on, RA1, RA2 and RA3 off. To zero the entire RAM memory space you may use either of two methods:

- 1) With "OK" in the ALPHA register (a precaution against accidental clearing), run 'CLRCM' in the Microbaud EPROM, or

- 2) Run 'ZR' from Appendix 2 with start address 8000 and end address 8FFF.

Now switch REN (RAM Enable) on (leave XASC off) and set up a null Function Address Table using "The ROM Adress Space" in Appendix 1 as a guide. You may like to give your pseudo-ROM RAM a name which will appear first in the CAT 2 listing. An example of this is also found in Appendix 1. You can now write, load and run your own machine language routines! To try out the MLI you may like to load some of the machine language routines which appear in Appendix 2.

## EPROM CURRENT DRAIN

Some brands of EPROM we have tried draw excessive amounts of current even when switched off - they have a very low impedance OE input which is high even when the MLT is unplugged, and so sinks about 50mA. Typically your MLT should draw around 100uA when unplugged. If you have an excessive current drain it can be fixed using the directions below.

First, cut the track coming from the pad at the top right of the 'L' EPROM. Connect the EPROM side of the cut track to the perimeter ground track using a piece of insulated wire. Next, cut three tracks, these being the track to the lower (cathode) lead of the LED, the track joining U28 pin 1 to +5V (on the rear of the PCB) and the track joining U28 pin 10 to ground.\* Then, connect U28 pin 10 to U16 pin 9 using a piece of thin wire. This is best done by joining the two pads on the rear of the PCB. Connect U28 pin 9 to the lower lead of the LED in the same way. Check to see that the EPROMS are still working normally.

APPENDIX 1

The ROM Address Space and The Function Address Table

ROM and RAM are <u>separate entities</u>, mutually exclusive.

RAM is addressed by 10-bit addresses for each 56-bit register (000 to 3FF).

ROM is addressed by 16-bit addresses for each 10-bit ROM word (0000 to FFFF).

```

Relative

Address

Function

X000

XROM Number

100X

Number of functions in the catalog (including module

name)

X002,

Address of ROM module name

X003

X004.

Address of first program

X005

X006,

Address of second program

X007

Address of 63rd program (if used)

X080.

180X

Next 2 bytes

2 Nulls (000, 000)

after last addr

Addr. of

Name of ROM (11 characters maximum)

ROM name

Addr. of

Function #1

Fon. #1

Addr. of

Function #2

Fcn. #2

XFF4 to

Special interrupt Jump locations

XFFA

XFFB to

ROM Name abbreviation and revision (i.e. CRID, WDIE)

XFFE

XFFF

8-bit checksum (for diagnostic module use)

```

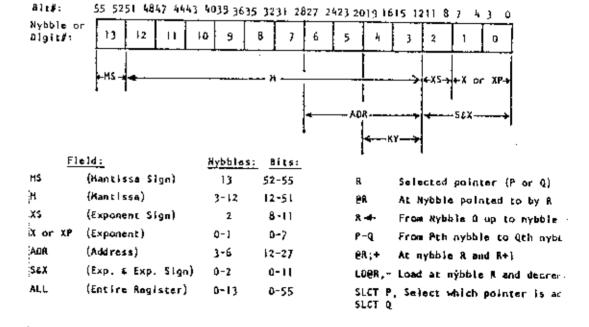

HP41 CPU Registers. Arrows indicate possible paths of data flow. Hote that the C register (56 bits long) is the main register through which information passes between RAM and EPU, as well as most CPU registers.

B1:#:

56 - BIT REGISTER FIELDS AND POINTERS IN THE HP41 INSTRUCTION SET. (5. Jacobs mormonic

The RAM name which appears first in the CAT 2 listing is simply a function name followed by a return, placed anywhere in the in the RAM. However, the name must be the first 'function' listed in the Function Address Table. Also note that all the function names are listed in reverse, as shown in this sample FAT and the Wand listing excerpt.

## A Sample FAT

| 8999 913                      | XROM 19                   |                         |

|-------------------------------|---------------------------|-------------------------|

| 8801 88F                      | 15 FUNCTIONS              |                         |

| 8692 861                      |                           | A Sample BATT -         |

| 8903 868                      | 80: 8168 -MICROBRUD-      | A Sample RAM Name       |

| 8004 899                      |                           |                         |

| 8 <del>99</del> 5 <b>9</b> 92 | 01: 8092 CSST             |                         |

| 8906 601                      |                           |                         |

| 8007-914                      | 02: 3114 LEFT             |                         |

| 8998 891                      |                           |                         |

| 8809 025                      | 93: 8125 GOOSE            |                         |

| 89 <b>0</b> 0 081             |                           |                         |

| 8998 92F                      | 84: 312F +1               |                         |

| 8000 001                      |                           | 8160 OAD "-"            |

| 808D 858                      | 85: 81 <b>59 R</b> ESETFL | 8161 004 °D"            |

| 899E 691                      |                           | 8162 015 <sub>"U"</sub> |

| 890F 072                      | 96: 8172 TPR              | 8163 001 "H"            |

| 8919 891                      |                           | 8164 002 *B*            |

| 8611 993                      | 97: 8183 TNX              | 8165 00F "O"            |

| 8812 991                      |                           | 8166 012 "R"            |

| 8913 88E                      | 08: 818E SF50             | 8167 003 °C"            |

| 8914 201                      |                           | 8168 009 -I.            |

| 8015 0A2                      | 99: 81A2 'DEMG            | 8169 00D "M"            |

| 8916 691                      | 48 4154 115               | 816A 02D                |

| 8917 9E6                      | 18: 81E6 UPDFAT           | 816B 3E0 R1N            |

| 8618 262<br>8819 822          | CL. cons. t.an            |                         |

| 881A 202                      | 11: 8222 **18             |                         |

| 8818 942                      | 12: 02:0 10:00            |                         |

| 891C 992                      | 12: 8242 'VER?            |                         |

| 801D 68B                      | 13: 828D CFX              |                         |

| 801E 865                      | 13 OCON CLY               | •                       |

| 801F 092                      | 14: 9292 SFX              |                         |

| 8928 888                      | 17. 9232 SEX              |                         |

| 8021 989                      | ·                         |                         |

|                               |                           | •                       |

|                               |                           |                         |

|     | 0        | 1 | 2            | 3 | 4 | 5      | 6 | 7 | 8 | 9 | A   | В | ¢           | D        | E                | F |

|-----|----------|---|--------------|---|---|--------|---|---|---|---|-----|---|-------------|----------|------------------|---|

| 00  | <u>@</u> | A | В            | Ç | D | E,     | F | G | Н | I | 3   | K | L           | М        | N                | 0 |

|     |          |   |              |   |   |        |   |   |   |   |     |   |             |          | <b>↑</b>         |   |

| 02  | S.A.     | ì | $\mathbf{n}$ | # | ş | 7.     | & | 1 | 4 | > | *   | + | <del></del> | -        | <del>&gt;-</del> | 1 |

| 03  | 0        | 7 | 2            | 3 | 4 | 5      | 6 | 7 | 8 | 9 | 25  | , | 4           | <b>u</b> | _                | ? |

| 0.4 | _        | • | -<br>h       |   | a | -<br>- | _ | ~ | ァ | ズ | 买   | 买 | ىر          | <b>≠</b> | Σ                | 4 |

| 04  | -        | a | Ü            | - | • | -      |   |   | • |   | * ` |   |             |          |                  |   |

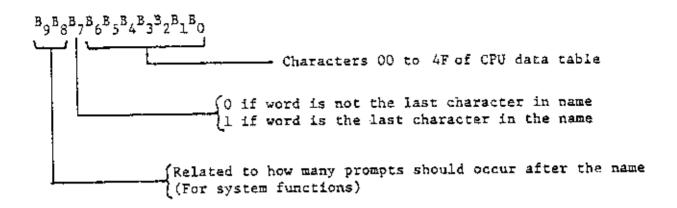

CPU Data Table for Non-last Characters of Machine Code Function Names

(For last character, add 080 hex to the code in the above table.)

## XROM User-Code Function Names:

If the program in question is user code, then the two words pointing to the program's address point to the first word in the program, which continues forward from that point. (This first instruction in the program would be an ALPHA label.) The two words previous to the pointed address may contain information related to the program's size for copying purposes, if this label is line 01 of the program.

| Example: | Addr.    | Code: | Function:      | Addr. | Codet | Function:    |

|----------|----------|-------|----------------|-------|-------|--------------|

|          | <u> </u> | OBE   | <del></del> "  | 406   | 057   | W            |

|          | OOE      | 204   | Addr. 402      | 407   | 04E   | N            |

|          | 00£      | 002   | for fcn.       | 408   | 044   | Ð            |

|          | OOF      | 004 2 | 202 20         | 409   | 054   | T            |

|          | •        | •     |                | 40A   | 053   | S            |

|          |          | 000   | O Page to cont | 40B   | 054   | T            |

|          | 400      | 009   | 9 Regs to copy | 40C   | 19C   | FIX          |

|          | 401      | 220   |                |       |       |              |

|          | → 402°   | 1C2   | LBL            | 4QD   | 000   | 0            |

|          | 403      | 001   |                | 40E   | 1A6   | XROM         |

|          |          |       | τ              | 40F   | 005   | 27,05 (WNDSC |

|          | 404      | OF7   | •              | 401   | 203   |              |

|          | 405      | 000   |                | -     |       | •            |

## APPENDIX 2

This Appendix contains some routines which are useful examples of machine language programming, its applications, speed and operation. The following is a brief description of each routine listed later in this section. We have included a smattering of various mithods of operation (for example immediate execute, programmable and non-programmable functions).

- CSST continuous single step. This routine is non-programmable and when executed it continuously single-steps through the current program, beginning at the current line. If flag 0 is set, CSST will step backwards, or this can be effected while you are stepping by pressig the 'ON' key. The 'ON' key toggles the stepping direction forwards or backwards. Each key apart from 'ON' and the backarrow (which exits the program) also has a stepping speed associated with it, moving down each column with £+ being the fastest down to R/S, then ALPHA, PRGM and finally USER being the slowest.

- SF50 These three routines are used by the user-level program "DEMO".

IEFT rotates the display left by one character, GOOSE places a left-facing goose in the display and SF50 sets flag 50 (surprise, surprise!), the message flag.

- "DETO" This user-level program shows some of the somewhat unusual (even in the realms of synthetics!) things which may be achieved using machine language. Running "DEFO" yields a left-facing goose flying right to left (minus the Wickes goose dropping). Local labels 10 to 14 have the following results:

IBL 10 - left goose flies left

LEL 11 - ALPHA register rotates left

LDL 12 - right goose flies left

LBL 13 - left goose flies right

IBL 14 - right goose flies right (as is normal)

- +1 This is an extremely simple routine which adds up by ones in machine language. Use it to impress your friends when compared to "+1R" run for the same length of time!

- "+1R" As for '+1', but in user code. Much, much slower!

- RESETFL Resets flags to MEMORY LOST status except flag 27 (USER) and flag 31 (TIME module DMY) are both set.

- TPR Prompting tone. This routine prompts for a 3-digit number and excutes the corresponding TCNE. This is not programmable.

- TNX Tone from X. A programmable funtion the same as "TN" in the PPC ROM.

- UPDFAT This updates the Function Address Table when new routines are inserted. Key the address of the new function (that is the address of the first executable word in the routine) into ALPHA, execute 'CODE', execute 'UPDFAT'. The FAT is updated by incrementing the number of functions and adding the routine address to the end of the FAT. If you had just keyed in the routine "TAX" at addresses 8180 to 8187, then to incorporate this routine in the FAT, type:

"8183", XEQ "CODE", XEQ "UPDFAT"

- "VER?" This routine returns the current mainframe ROM revisions.

- CFX Clears the flag given by the value in X which can range from \$0 to 55.

- SFX Sets the flag specified by the number in the X-register. As for CFX, this can be any flag in the system.

| 808E 094 'T'                         |                                                     |

|--------------------------------------|-----------------------------------------------------|

| 868F 913 "S"                         | 8010 002 PMCGD 00C7                                 |

| 8898 813 'S'                         | 88D1 266 C=C-1 StX                                  |

| 8891 893 °C-                         | 8002 308 JNC 80C0 -05                               |

| 8892 888 NOP                         | 90D3 181                                            |

| 8093 22D                             | 80 <b>04</b> 878 PNCXQ 1060                         |

| 6894 6A8 2NCXQ 2A88                  | 89D5 93C                                            |

| 8895 34C ?FSET 12                    | 8906 261                                            |

| 8836 211                             | 8007 000 PNCXQ 0098                                 |

| 8897 887 2CGO 2184                   | 8008 273 JNC 80A6 -32<br>8009 11A 8≃C M             |

| 8098 05A C≈0 M                       | 99BA 91C R= 3                                       |

| 8899 95C R= 4                        | 8808 1E2 C=C+C QR                                   |

| 9 <b>999 050 LBER 1</b>              | 800C 127 JC 8100 +24                                |

| 8098 170 PUSH ADR                    | 8000 65A C=8 M                                      |

| 8890 023 JHC 8090 +04                | 89DE 95C R≈ 4                                       |

| 809D 3F8 READ 15(e)                  | 89DF 050 LD0R (                                     |

| 899E 381                             | 80E0 1DA 8=A-C M                                    |

| 889F 040 ?HCXQ 28E6                  | 80E1 31A ?A(C M                                     |

| 98A8 3C4 ST=0                        | 80E2 023 JNC 38E6 +84                               |

| 88A1 184 CLRF 8                      | 80E3 88A AC>C M                                     |

| 8992 196 A=C SLX                     | 8864 178 PUSH ABR                                   |

| 8883 886 B=A S&X                     | 99E5 388 JNC 80D6 -0F                               |

| 8994 105<br>8995 814 ?NCXQ 8571      | 8866 219 LDAR 8                                     |

| 8986 94E C=9 ALL                     | 88E7 1DA A=A-C M                                    |

| 8847 138 LDI SEX                     | 88E8 319 ?RKC N                                     |

| 8888 8C3                             | 88E9 3D7 JC 86E3 -06                                |

| 8849 18C RCR 11                      | 89EA 95C R≈ 4                                       |

| 89AA 19E A≃C ALL                     | 89EB 119 LD <b>e</b> R 4                            |

| SOAB 180 POP ADR                     | SØEC AIA LD <del>e</del> R A                        |

| 88AC 178 PUSH ADR                    | 88ED 1DA A=A-C M                                    |

| 89AB 130 LDI SAX                     | 80EE 05C R= 4                                       |

| 889E 01F                             | 80EF 950 LDGR (                                     |

| 80AF 3CC ?KEY                        | 80F0 31A 24KC M                                     |

| 8880 907 JC 9003 +18                 | 89F1 918 JNC 89F4 +63                               |

| 8801 266 C=C-1 S&X                   | 89F2 88A A()C M                                     |

| 8082 3EB JNC 89AF -03                | 88F3 858 JHC 88FE +98                               |

| 8083 279 C=C-1 M                     | 89F4 1DA A=A-C M<br>89F5 31A ?A <c m<="" td=""></c> |

| 89B4 3CB JNC 89AD -07                | 80F6 818 JNC 68F9 +03                               |

| 8800 388 KEND [4(8)                  | 80F7 08A A<>C M                                     |

| 8086 IFE C≃C+C MS                    | 88F8 828 JHC 88FT +85                               |

| 80B7 337 JC 809D -1A                 | 88F9 85C R= 4                                       |

| 8988 149                             | 80FR 002 A=0 @R                                     |

| 88B9 9A4 ?NCXQ 2952                  | 89F8 08A AK>C M                                     |

| 888A 3F8 READ (5(e)                  | SOFC IFA C=C+C #                                    |

| 898B 144 CLRF 6<br>80BC 2E6 ?C≠0 S&X | 99FD IFA C=C+C M                                    |

| 898B 3DD                             | 80FE 1FA C=C+C K                                    |

| 80BE 0A9 ?CXQ 2AF7                   | 80FF 328 UNC 80E4 -18                               |

| 800F CDD                             | 8100 388 READ (4(d)                                 |

| 89C8 88C ?MCXQ 2337                  | 8191 2FC RCR 13                                     |

| B9C1 3F8 READ 15(e)                  | 9192 318 C(>\$T XP                                  |

| 88C2 226 C=C+1 S4X                   | 8193 09C ?FSET 3                                    |

| 88C3 14C ?FSET 6                     | 8184 816 JNC 8187 +83                               |

| 89C4 013 JNC 80C6 +02                | 8185 004 CLRF 3                                     |

| 90C5 646 C=0 S&X                     | 8196 913 JNC 8198 +82                               |

| 8806 3E8 WRIT 15(e)                  | 8187 808 SETF 3                                     |

| 89C7 2CB JNC 89A9 -27                | 8109 308 C()ST XP                                   |

| 9878 CCA F=K51 K1                    | 8199 33C RCR 1                                      |

| 99C9 37A ?A≠C M                      | 810A 3A8 WRIT 14(d)                                 |

| 99CA 97F JC 80D9 +8F                 | 8188 171<br>8180 GLC SUCYA ASEA                     |

| 80CB 130 LDI S&X                     | 8190 010 ?NCXQ 6750<br>8100 248 JNC 8006 -37        |

| \$8CC 3C8                            | 0100 210 MIC 8886 -37                               |

9860 308 CLRKEY 9862 300 PKEY 1001 718

8118 894 °T° 8111 996 "F" 8112 805 °E\* 8113 800 °L° 8114 139 LDI S&X 8115 919 8116 270 RAM SLCT 8117 130 LDI S&X 8118 9FD 3119 3F0 PRPH SLCT 811A 999 HOP 8118 3F8 READ 15(e) 8110 84E C=8 ALL 811D 3F0 PRPH SLCT 811E 270 RAM SLCT 811F 3E0 RTM

8128 985 \*E\*

8121 913 \*S\*

8122 99F \*O\*

8123 89F \*O\*

8124 997 \*G\*

8125 3C1

8126 988 PHCXQ 2CF8

8127 139 LDI S&X

8123 92C

8129 3A8 WRIT 14(d)

8128 924 PHCXQ 9953

812C 3E8 RTN

8120 981 ·1· 812E 02B \*+\* 812F 04E C=0 ALL 8138 2RB SETBEC 8131 278 RAM SLCT 8132 23A C=C+1 M 8133 300 SKEA 8134 3F3 JNC 8132 -92 8135 130 LDI SEX 8136 989 8137 18E R=C ALL 8138 35C R= 12 8139 1A6 A=A-1 S&X 813A 3FA LSHFA N 8138 342 ?A≠9 @R 813C 3EB JNC 8139 -83 813D BRE ACXC ALL 813E 8E8 WRIT 3(X) 813F 3C8 CLRKEY 8148 3CC ?KEY 8141 3F7 JC 813F -82 8142 3E8 RTN

|                     | į.                                     |                           |

|---------------------|----------------------------------------|---------------------------|

| -2149 08C *L*       | 0152 004 070                           |                           |

| 3149 886 "F"        | 81E8 894 °T°<br>81E1 881 °A°           | 81.LBL -DEMO-             |

| 8148 814 -1-        | 8152 996 •F*                           | 92+LB4, 18                |

| 8140 085 °E"        | 81E3 804 -D-                           | 83 GOUSE                  |

| 8149 013 "S"        | 81E4 818 *P*                           | 94 SF58                   |

| 814E 905 -£-        |                                        | 95+LBL 91                 |

| 814F 912 -R-        | 81E5 015 *IJ*                          | 96 LEFT                   |

| 8150 04E C=0 ALL    | 91E6 0F3 READ 3(X)                     | 97 9                      |

| 8151 270 RAM SLCT   | 81E7 846 C=8 S&X<br>81E8 226 C=C+1 S&X | 98 GTO 81                 |

| 8152 29C R= 7       | 81E9 1BC RCR 11                        | 99+LBL 11                 |

| 8153 600 LDGR 3     | 81EA 330 FETCH SAX                     | 10 UAIEH                  |

| 8154 350 LDER D     | 81EB 186 R=C S4X                       | 11+LBL 02                 |

| 3155 05C R= 4       | 81EC 226 C=C+1 S&X                     | 12 LEFT                   |

| 8156 110 LD@R 4     | BIED 848 NROM                          | 13 9                      |

| 8157 210 LDBR 8     | SIEE 03C RER 3                         | 14 GTO 82                 |

| 3158 398 WRIT 14(d) | 81EF BAG ACCC S&X                      | 15+LBL 12                 |

| 8159 3E0 RTH        | 81F0 226 C=C+1 S4X                     | 16 SF50                   |

| 0103 SEO RIN        | 81F1 1E6 C=C+C SLX                     | 17+LBL 03                 |

| i                   | 81F2 1BC RCR 11                        | 18 LEFT                   |

|                     | 81F3 646 C=9 SLX                       | 19 8                      |

|                     | 81F4 10E A=C ALL                       | 29 GTO 93                 |

|                     | 81F5 0F8 READ 3(X)                     | 21.481 13                 |

|                     | 81F6 05E C=0 MS                        | 22 G00SE                  |

| 0165 805 -0-        | 81F7 85A C=0 M                         | 230LBL 04                 |

| 816F 092 "R"        | 81F8 31C R= 1                          | 24 0                      |

| 8179 119 °P*        | 81F9 BEA CC>B RC                       | 25 GTO 94                 |

| 8171 114 "I"        | 81FA 04A C=0 R<                        | 26•LBL 14                 |

| 8172 <b>800 NOP</b> | 81FB 23C RCR 2                         | 27 9                      |

| 8173 8A6 AK>C S&X   | 81FC 21A C=C+9 M                       | 28 GTO 14                 |

| 8174 38B            | 81FD <b>840 W</b> ROM                  | 29 END                    |

| 8175 05A ?NCGO 16E3 | 91FE 84E C=9 ALL                       | <u> </u>                  |

| 1                   | 81FF OCA C=8 R<                        |                           |

|                     | \$208 23A C=C+[ N                      |                           |

| 1                   | 9291 219 €=C+R M                       | 01+LBL -VER?-             |

| 3180 093 -X-        | 8282 040 WROM                          | 92 -6+-                   |

| 8181 00E -N-        | 9203 046 C=0 S&X                       | 03 RCL (                  |

| 8182 014 -T-        | 82 <del>8</del> 4 238 C≃C+1 N          | 84 ENTER+                 |

| 8183 9F8 PEAD 3(X)  | 8295 040 WROM                          | 95 ENTER+                 |

| 184 380             | 8206 23A C=C+  M                       | 06 ENTERT                 |

| 8185 008 PHCXQ 02E3 | 8207 949 WROM                          | 97 * <del>*</del> *       |

| 8186 393            | #2 <b>98 3E0 RTN</b>                   | 88 RCL [                  |

| 8187 95R ?HCGO 16E3 |                                        | 99 "ROM 012: -            |

|                     |                                        | 18 XEQ 81<br>11 XEQ 81    |

|                     |                                        | = -                       |

|                     |                                        | 12 XEQ 01<br>13 RVIEN     |

|                     | 01+LBL -+1R-                           | 14 RTN                    |

| 819A 080 *0*        | 92 1                                   | 15+LBL #1                 |

| 8188 035 151        | 93 ENTER+                              | 16 ENTER+                 |

| 818C 006 °F"        | 94 ENTERT                              | 17 RONX                   |

| 818B 913 "S"        | 05 ENTERT                              | 18 BIH>8cD                |

| 818E 388 READ 14(d) | 96 PUSH R/S-                           | 19 64                     |

| 818F 3D8 C()ST XP   | 87 PROMPT                              | 28 +                      |

| 8198 088 SETF 5     | 98+LBL 91                              | 21 XXA SYNTHETIC TEXT LIN |

| 8191 3D8 C<>ST XP   | 89 +                                   | 22 CLX                    |

| 8192 388 WRIT 14(d) | IO CTO 01                              | 23 RCL Y 82 F2 18 88      |

| 8193 3E0 RTH        | 11 END                                 | 24 RDN 97 F1 8F F-E       |

|                     | 771.8                                  | 25 X+Y                    |

|                     | İ                                      | 26 RTH                    |

|                     |                                        | 27 END                    |

|                     |                                        | -· <b>-</b> ·             |

```

8240 899 °o*

8241 270 °p*

8242 106 FF

8243 000 ***

8244 BFS "u"

289 098 -X-

8245 000 "*"

288 886 F

8246 056 "Y"

29C 003 °C*

8247 045 °E*

280 244 CLRF 9

8248 952 'R"

28E 82B JNC 8293 +85

8249 93F *?*

28F 898 X

8249 1F2 "r"

298 886 °F*

824B @L0 *9*

291 813 S

8240 888 ***

292 248 SETF 9

8240 198 *9*

293 0F8 REAR 3(X)

824E 075 "u"

294 39B

824F 183 "+"

295 008 PHCX0 02E3

8259 183 °+°

2% 00E A=8 ALL

8251 183 ***

297 106 A≕C S&X

8252 1F2 "r"

298 130 LDI S&X

8253 89F **

99 938

8254 OFE "€"

290 306 ?AKC S&X

8255 196 *8*

98 38i

8256 075 "u"

290 88A ?HCGO 82EB

8257 1F9 "y"

90 130 LBI SAX

8258 952 R1

9E 888

3259 04F 101

1996 BEE C<>B ALL

825A 94D 'K'

200 84€ C≃9 ALL

8258 929 * *

201 270 RAN SECT

8250 638 181

202 ?2E C≂C+1 ALL

825B 031 "1"

203 23C RCR 2

825E 032 -2*

201 186 A=A-B S&X

825F 03A *:*

-106 3F3 JNC 82A3 -02

8269 929 * *

206 913 JNC 8298 +82

8261 1E0 ***

997 IEE C=C+C ALL

8262 99A **

DOS 166 R=A+1 SLX

8263 981 "*"

M9 3F3 JNC 82A7 -02

8264 188 ***

MA GEE CKYB ALL

8265 997 "4"

MB 388 READ 14(d)

8266 881 "*"

MC ORE AKYC RLL

8267 160 ***

b01 24C ?FSET 9

8268 004 'e"

20E 82B JNC 82B3 +95

8269 081 ***

MF BEE C<>8 ALL

826R 17E "E"

269 379 C≕C OR A

8268 185 °B*

261 999 NOP

826C 102 *X*

982 823 JNC 8286 +84

826D 183 '+'

183 GCE C=8 ALL

826E 185 "%"

MB4 2AE C=-C-1 ALL

826F 862 %

1285 3890 C∓C AN+D A

8270 195 -4-

26% 3498 HRJT 14(d)

8271 049 -1-

287 149

8272 116 °ā1

289 859 ?NCCO 1652

8273 914 °a*

8274 140 °E*

8275 195 ***

8276 847 °G*

8277 177 "v"

8278 198 "8"

8279 076 "p"

8278 175 fuf

827B 1A5 ***

827C 96A 1j*

827D 185 *$*

827E 108 "H"

```

827F 998 "A" 8288 22F "/"

BYTE LISTING OF -DEMO-8100 008 "A" 81A1 219 -9-81A2 1C4 \*D\* 8183 801 \*\*\* 8184 8F5 "u" BYTE LISTING OF -+1R-8185 969 \*\*\* 8196 944 °B\* 8228 084 'a" 8197 645 'E' 8221 278 'p" 8198 946 "M" 8222 106 "F" 8199 04F \*0\* 8223 898 \*\*\* 81AA 10B "\" 8224 0F4 "t" 8188 184 "\$" 8225 999 \*\*\* 81AC 9C3 \*C\* 8556 058 .+. 81AD 184 \*\*\* 8227 031 11 819E 9C8 "H" 8228 952 "R" 81AF 192 'X' 8229 111 -0-8188 IR4 \*\*\* 8229 183 161 8181 002 "B" 822B 183 \*\*\* 81B2 119 -0-8220 183 \*\*\* 8183 182 -2-8220 1F8 "x" 8184 086 -F-822E 858 \*P\* 8185 190 "y" 822F 955 \*U\* 8186 17E "E" 8238 953 ·S· \*\*\* E91 7818 8231 048 "H" 8188 LA4 \*\*\* 8232 020 • • 8189 0C2 -B-8233 952 -R-8189 116 \*6\* 8234 82F \*/\* 81BB 1B3 -3-8235 853 \*\$\* 81BC 696 \*f\* 8236 18E 11 81B0 190 -4-8237 102 -¥-81BE 184 "\$" 8238 140 '6" 81BF 9C8 \*H\* 8239 182 \*2\* 8109 184 a. 923A 804 "a" 8101 1R4 \*5\* 8238 103 THT 81C2 OC2 -8-823C 983 \*+\* 81C3 110 -6-8233 22F -/-81C4 1B4 -4-8105 996 "F" 81C6 10E \*\*\* 81C7 184 "\$" 8108 **6**03 °C\* 81C9 185 \*#\* 81CA 110 \*8\* 81C8 185 ·5· 81CC 984 \*a\* 81CD 10F \*\*\* 81CE (19 '8" 81CF 1BF \*?\* 8100 004 fer 81D1 1CA •J• 81D2 006 °C\* 81D3 22F -/-

## APPENDIX 3

## Other sources of information

This Machine Language Interface is based upon the Machine Language Development Laboratory designed by Lynn A. Wilkins (7344). This design was published in the PPC Calculator Journal V 9 N 3. This article gives more details on the construction of the MIDL, although this is intended for use with a wire-wrapped board, as opposed to the printed wiring board type of construction used for the MLL.

The available literature on the subject of microcode, is very extensive, but almost inaccessible outside the major programmable calculator user group in the world, PPC. This group was formed in 1974 when the first handheld programable calculator, the HP-65, was released by Hewlett-Packard. It was then known as the 65 User's club, changed its name to the PPC Club in 1978, and was incorporated in 1982. Amongst a wide range of other activities, it publishes what was originally called 65 Notes, but became the PPC Calculator Journal. There was no information on microcode (the name originally given by HP to the various assembly language, or machine codes of their generations of hand held calculators, both programmable and non-programmable) outside of the pages of the PPC Journal (and the 65 Notes), until 1980. The Melbourne Chapter of the PPC Club, PPC Melbourne, started the publication of its own user's publication, PPC Technical Notes, in 1979, and has printing information on the subject from 1980 on.

The PPC Journal is available only to members of the PPC Club, at an annual subscription which varies around the world. For a sample copy, and membership application forms, write to:

PPC, 2545 West Camden Place, Santa Ana, California, U.S.A. 92704, enclosing an A4 sized self-addressed stamped envelope (two ounces, airmail, or International stamp vouchers for the appropriate amount). The same material is available from PPC Melbourne.

Subscriptions to PPC Technical Notes are A\$20 annually, and back issues are available at A\$10 per set, plus postage. (Airmail rates on back issues run to well over A\$10, depending on the destination.) Send Bank Cheques or money orders, made payable to PPC Melbourne, to:

R.M. Eades, Box 15, Hampton, Victoria, Australia 3188

Only the essential references are given here. For further reading relating to the subject, see back issues of the PPC Journal, and PPC Technical Notes. Anyone wanting to program in the HP-41c/cV microcode should have a good grasp of the operating system of that machine. Suitable texts are:

- Wickes, W.C. Synthetic Programming on the HP-41c. (Larken Publications, 4517 NW Queens Ave., Corvallis, Oregon, U.S.A. 97330.)

- Jarett, K. HP-41 Synthatic Programming Made Easy. (SYNTHETIX, 1540 Mathews Ave., Manhattan Beach, California, U.S.A., 90266-)

- Dodin, J-D. Au Fond de la HP-41c. (In French.) (J-D. Dodin, 77 Rue du Cagire, 31100 Toulouse, France.)

The latter is (to date) the only publication to give an elementary introduction to the operating system of the HP-41c, and to the subject of synthetic programming, a knowledge of which is essential to serious microcode work, outside the walls of Hewlett-Packard.

## APPENDIX 4

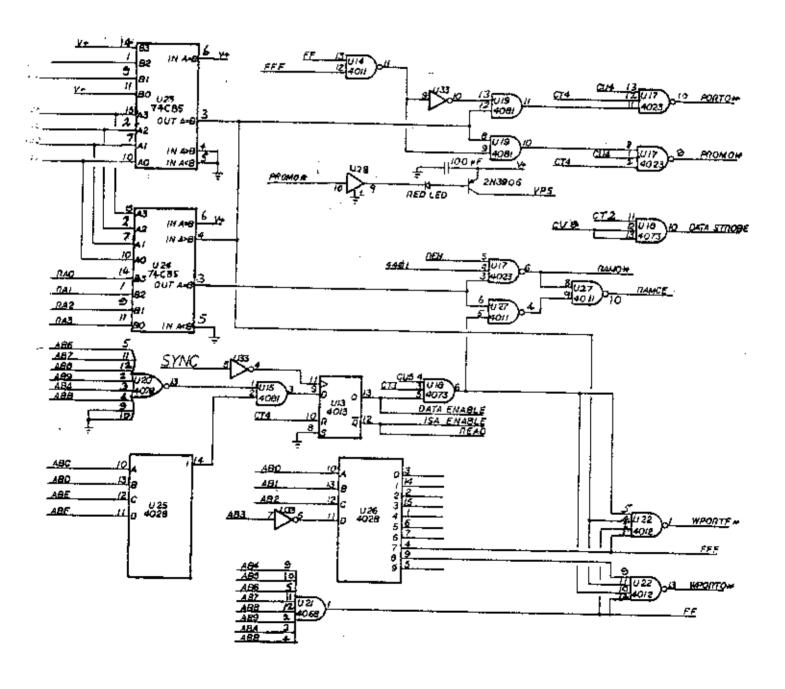

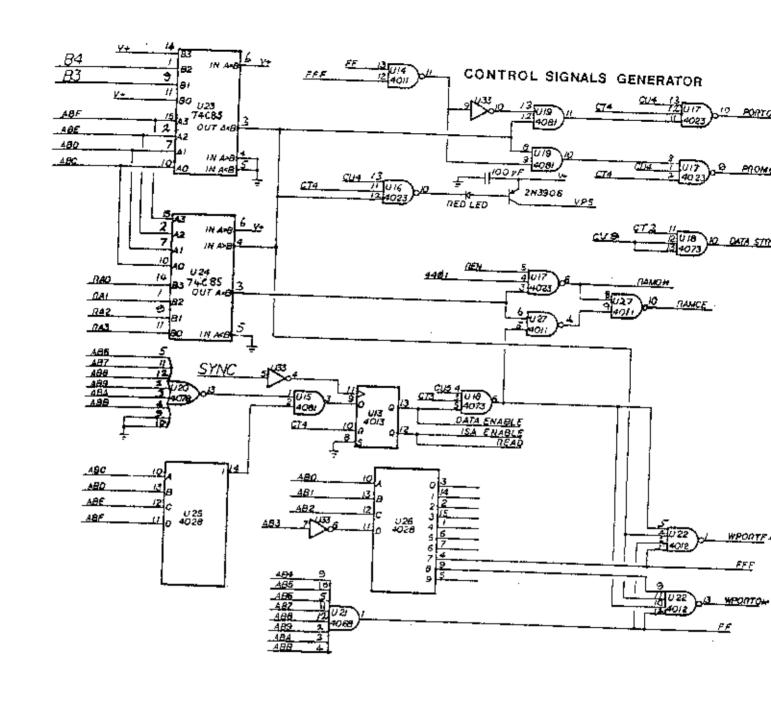

## CONTROL SIGNALS GENERATOR

(After EPROM Power Supply modifications.)

## Microbaud

## Developments

## MACHINE LANGUAGE INTERFACE

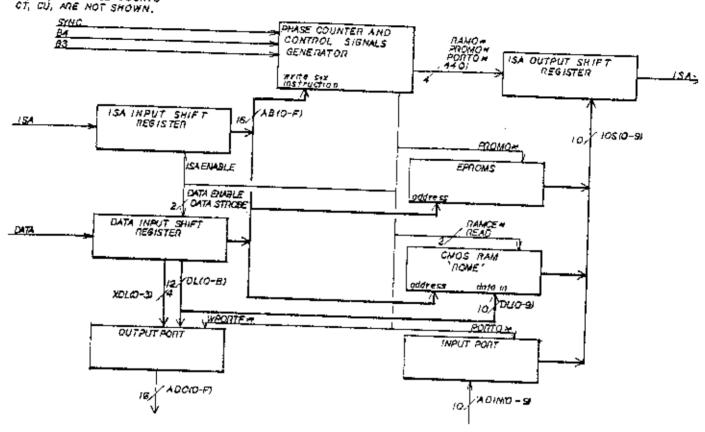

BLOCK DIAGRAM SHOWING DATA AND CONTROL PATHS. DI, 92,AND PHASE COUNTS OT, CU, ARE NOT SHOWN.

HP-41 MACHINE LANGUAGE DEVELOPMENT LAB - MLDL

## INTRODUCTION TO THE MLDL

I built the Machine Language Development Lab for a toy so that I could play with the inner language of the IP-41. When it turned out that other members of PPC also wanted to toy with the calculator's inner secrets (surprise, surprise!) I decided to release the design for noncommercial use. The introduction of EPROM boxes also spured the MLDL project. Some PPCers will want their very own machine code in EPROM. But it is very difficult to develop machine code without a reasonable way to test it. The MLDL is small. It is portable. It is easy to use. And it allows the immediate testing of machine language code.

There are other, more powerful, ways to develop code. For instance, Paul Lind (6157) uses a micro-computer and a dual port RAM card. The computer sees the shared RAM as a pair of I/O ports. The NP-41 sees the

RAM as if it were a ROM Module. Faul can use all the gower of his computer to design code for the RP-41. He has an editor, assembler, disk storage, trace routines, ... the works. (A package of schematics is available for a newinal fee. For the details send a SASE to Faul c/o Puget Sound Programing, P.O. Box 5929, Scattle WA 98105)

The MLDL provides three functions. There is an EPROM array to store the special functions useful to the MLDL. There is an I/O port which is to be used with an EPROM programmer. And there is a CMOS memory array. The CMOS array is called NOME for ROM Experimental. ROME is where machine code can be loaded and tested.

The 4K words of MPROM in the current design are adequate for a small assembler and support functions. More EPROM could be added. 16K total would be no problem. But the commercial EPROM boxes are probably more convenient.

The I/O port may prove to be unnecessary when someone starts selling an EPNOM programmer that runs on the HP-IL. Don Robinson (8021) tells me that he has such a device. Also, there may be some users who will run their code from the MLDL. They may never make hard copies in EPROM.

The 4K words of ROME is a lot. Most machine code routines will be one hundred to two hundred words long. There is room for a lot of programing in four thousand words!

The MLDL is a convenient, inexpensive tool to help write and test RP-41 Machine Language code. There is probably only a handful of PPC members outside of HP who have been able to run their own machine code. Well, now is your chance too.

## MACHINE CODE, MICRO-CODE, OR M-CODE?

Let me identify the three types of code used in the ep-41.

- USER CODE

- TRANSLATED USER CODE

- · MACHINE CODE

User Code is what HP describes in the HP-41C/CV user manual. It is the code that same, rational, ordinary calculator users use. User Code will satisify 99% of user needs. Synthetic Programming, since it has been accepted by MP, is User Code that will satisfy another 0.9% of user needs. User Code is good, useful stuff.

Translated User Code is one type of code usable in ROMs and EPROMs. T-Code is User Code which has been modified to fit the ten bit ROM word format. The PPO ROM was initially User Code. It was part of HP's service when producing the custom ROM to provide the modification. T-Code can be identified as ROM code which can be COPYed into user memory.

Machine Code is the other type of code usable in ROMs and EPROMs. Machine Code is the native language of the micro-processor used within the HF-41C/CV. The code is not properly called micro-code. Micro-code or "micro-programme" is a sequence of operations used to control that part of a computing "...machine which supplies the pulses for operating the gates associated with the arithemitical and control registers. "(M.V. Wilkes, The Best Way To Design An Automatic Calculating Machine.)" Calling Machine Code "micro-code" is wrong. But almost everybody does it. I shall use the compromise term M-Code.

## UNDERSTANDING THE MLDL

This is a 'broad brush' description of how the MLDL works, just as the Block Diagram is a large scalo picture. Details of the individual blocks are given in the BUILDING AND CHECK-OUT section of this article. The necessary background to understand the MLDL/HP-4U interface is in two PPC Journal articles. DeArras' PPC V7N3 and McClellan's PPC V6N6.

It is all very simple. The purpose of the logic chips is to shift out the proper hits at the proper time.

The ten bit M-Code words which are shifted out the ISA line to the KF-41 originate in the EPROM, ROME, or the Input Port. The Address Bus lines AM(C-F) determine which is selected. During a machine cycle sixteen bits of ROM address is shifted out of the HP-41 on the ISA line. The Isa Input Shift Register takes in the address bits and latches them. ISA ENABLE gates the

captured address onto the Address Bus, Comparator circuits in the Control Signals Generator look for a match with either the MPROM address, the ROME address, or the Input Port address. If a match is detected one or the Input Port address. It a match is detected one of the control signals RAMO\*, PROMO\*, or PORTO\* is asserted and at the proper time the Isa Output Shift Register is loaded with the ten bit M-Code which is on IOS(0-9). Then the word is shifted out. The source IOS(0-9). Then the word is shifted out. The source of the M-code is enabled by the control signals RAMCE\* ANDER with READ, or PROMO\*, or PORTO\*.

It is obvious how the ten bit Machine Code words get it is covious now the ten bit machine code words get into the EPROM and the Input Port. The ROME isn't so obvious. The ROME is loaded in response to a special wRITE 56x instruction, 040. The instruction is a NOP to the HP-41 so it does nothing during the following machine cycle. The MLDL interprets the instruction magnine cycle. The ALDL interprets the instruction and uses the DATA bits as a source of address and code word. The MLDL writes the code word at the address. The C register out of the HP-41 CPU is repeatedly latched into the Data Input Shift Register. It is latched into the Data Input Shift Register. It is latched at the phase where the least significant bit of C becomes DLO. Thus the lowest ten bits of C become the ten bit word loaded into the ROME. Every instruction out of the HP-41 is latched into the Isa Input Shift Register and sent via the Address Bus AB(6-F) to the Control Signals Generator. The wRITI 56x is decoded and the most significant bits of the The wRiTE beta Imput Shift Register are gated onto the Address Bus AB(0-F). Data Lines DL(0-9) are also gated to the ROME imputs. READ is not asserted, a write, and when RAMCE\* is asserted the ten bit word on DL(0-9) is written into the ROME.

#### BUILDING AND CHECK-OUT

It is not difficult to build the MLDL. The builder should have some experience constructing electronic projects. If you intend to build the MLDL yourself, 'perfboard,' 'wire wrap,' and 'bypass cap' should be familiar terms. If you don't know which side of an IC is up, find somebody who does. A familiarity with digital logic will be a provided the statement of t digital logic will almost guarantee a working MLDL.

Most of the ICs used are detailed in the RCA COS/MOS

Integrated Circuits Data Book, 55D-250B. The details

may also be in data books from other IC manufacturers.

Let's establish some ground rules. ICs are identified by the U number or generic part number. For exame C16 1s a 402s. Particular IC pins are identified by the U number or generic part number. For example, C16 is a 4029. Particular IC pins are identified by appending the pin number to the associated U number. Pins 2 and 4 of U16 are called out as U16-2.4. Signal names are in capital letters. For example, ISA or PROMO\*. The associated function is logically assorted when the signal voltage is high. But, if the name is followed by the asterisk the function is asserted when the signal voltage is low. PROMO\* is asserted when the signal voltage. For a signal group I may use the short notation AB or AB(0-F) instead of ABO thru app. For example,

The MLDL was designed for easy modular construction. An oscilloscope will facilitate check-out, but should not be necessary. A simple logic probe will suffice (unless you've really got your wires crossed.) The (unless you've really got your wires crossed.) The instructions proceed in sections. Each section will call for the wiring and check-out of a modular block of circuits. The check-out also goes into the 'how and why' of each block's operation. Because some ICs are used in more than one block not all the inputs to the IC will be wired. For example, Ul3 is used in the law Dutput Shift Register and the Control Signals isa Dutput Shift Register and the Control Signals Generator. Wire the unused inputs of all ICs to ground. I use a contrasting wire tolor for this. It helps in finding the inputs later. Install only the ICs which are wired. Proceeding block-by-block will help catch miswires before they are hopelessly buried. The approach also provides positive (I hope) reinforcement and confidence.

Each section calls for:

- Organizing the parts layout.

Wiring the circuits together as shown on the schematic.

- 3. Double checking the wiring. Make sure the

- unused inputs are tied low.

4. Installing the ICs.

5. Verifying the black's operation.

Steps 1 and 5 are the thinking steps. between demand care and attention. The most likely problems will be miswires or shorts. The next most likely problem is a misuadcrstanding of how a block as supposed to operate. The block may work perfectly but you might think otherwise. Talk it over with a friend. The last thing to assumm is bad parts. I do know how

very frustrating it can be to search out the causes of problems. I sympathize with your difficulty when the problems. I sympathize with your difficulty when the verify step doesn't, but it is impractical for me to personally aid you. Be not call me. You are on your own. I would appreciate a letter describing in detail any problem you may have when building the MLDL. I will keep a twoord of such problems and if common problems develop I will try to assess the causes and publish fixes. I would also like to read about your guddê6669.

Section 1. The Plug. The plug which connects the HP-41 to the HLDL is vital to the success of the project. The finished connector/cable assembly must be rugged. You rinished connector/cable assembly must be rugged. You will be plugging and unplugging the MLDL often. I recommend and old memory moduls which can be opened at the seam. Unsolder and throw out the circuit board. Use ribbon cable or single wires to connect to the MLDL. I recommend a DIP plug at the MLDL end. I used a sixteen pin plug into a wire wrap socket on the prototype. The socket had the following pin outs.

| V+   | 1        | 16 | B4   |

|------|----------|----|------|

| VCC  | 2        | 15 | в3   |

| GND  | 3        | 14 | PWO  |

| _    | 4        | 13 |      |

|      | 5        | 12 |      |

| DATA | 5        | 11 | PIN  |

| ISA  | 7        | 10 | SYNC |

| Ø2   | В        | 9  | øl   |

|      | <u> </u> |    |      |

The length of the cable is important. Don't try to compete with Ma Bell. Be warned that the longer the wires the more likely will be electro-static caused crashes. The MD-Ale that have been applied to the MD-Ale that the crashes. The HP-41s that have been used with the prototype MLDL had no trouble driving eighteen inches of wire. The verification of this section is to double check the wiring for continuity and mechanical integrity. Be sure to identify the wires at the MLDL and. Glue the memory module back together and set the cable assembly aside.

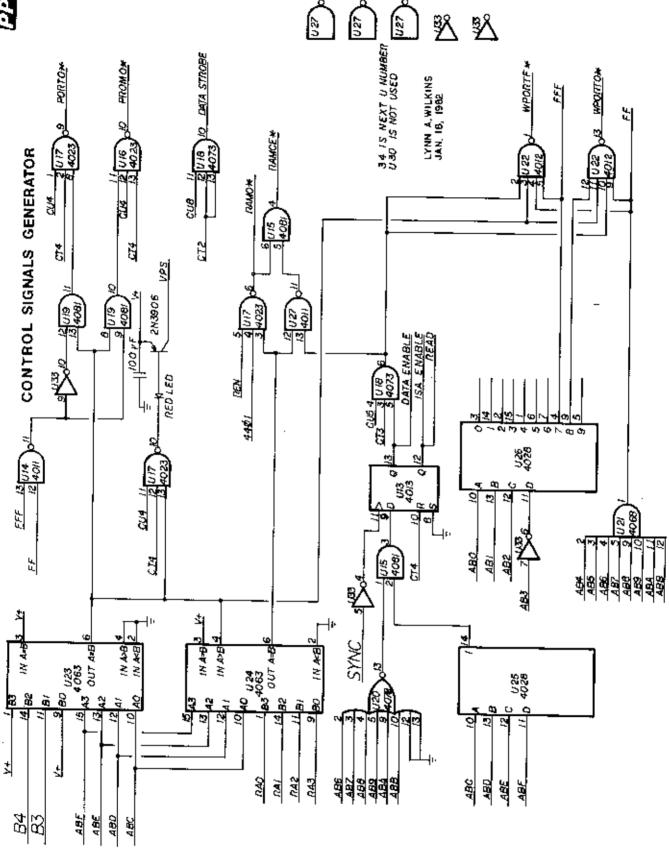

Scotion 2. The ROME battery and the EPROM power switch. ODDS AND ENDS shows a battery and diode circuit. The batteries are there to maintain the CMOS memory while the MLDL is not connected to the memory while the MUDL is not connected to the calculator. Three AA cells should keep the MLDL alive for the shelf life of the batteries. Replace them when the total voltage to the memories drops to 2.1 volts. The 100 micro-farad capacitor will supply the MLDL while you change the batteries. Just Son't take all day. The Control Signals Generator shows a NES control signals Generator shows a the MLDL while you change the batteries. Just con't take all day. The Control Signals Generator shows a VPS control circuit comprising a 203906 transistor, a red light-emitting-diode and the 100 micro-farad capacitor. VPS is the power for the EPROMS. The transistor is the switch which turns the VPS on for the time that the EPROMS are used. Because VPS is on for only one phase time, speeded up HP-41s may not work with the MLDL, Without the switch the EPROMS would consume hundreds of milli-amps and overload the calculator's power supply. The red LED provides a certain voltage drop which helps match the output certain voltage drop which helps match the output voltage/current characteristic of the CMOS gate, Ul7, with the drive requirements of the 2N3906. Any simple red LED will work, I used a MV50 type. By the way, don't expect to see the LED light whenever the EPROM is accessed. If it does light, something is wrong. The battery and VPS control circuits are simple enough to vertice by simply checking the continuity. Checking to verify by simply checking the continuity, checking the diode polarity, and checking the emitter-base-collector connections on the transistor.

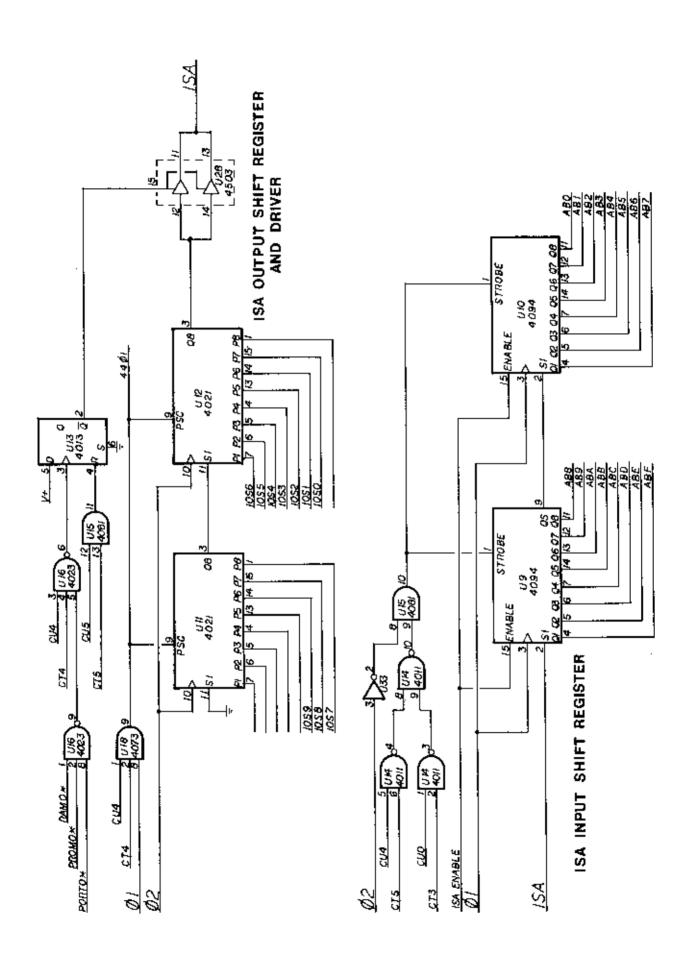

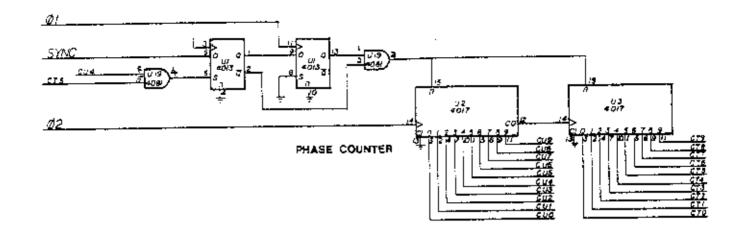

Section 3. The Phase Counter. Recall that the HP-41 uses a fifty-six phase machine cycle. The Phase Counter maintains synchronism between the NLDL and the Counter maintains synchronish between the MLDL and the HP-41. For example, ANDing the output of the Tens Counter CT5, U3-1, with the output of the Units Counter CU4, U2-10, generates a pulse in synch with the fifty-fourth phase. The pulse is used to reset the Phase Counter whenever a SYNC is missing. The HP-41 generates a SYNC only when fetching a ROW instruction opcode. SYNC is suppressed when the HP-41 fetches an immediate operand or executes a FETCH 55%. The last falling edge of SYNC resets the phase counter The last falling edge of SYNC resets the phase counter and forces synchronism with the calculator. Note that the phase numbers used in the MLDL are shifted from those used in the DeArras article. It is a good exercise to determine which way. Double check the those used in the DeArras article, It is a good exercise to determine which way. Double check the wiring of D1, U2, U3, and U19 (This is the last warning about the unused inputs. Tie them low.) The time has come to connect the MLDD to the HP-41. Don't expect a lot yet. Press and hold down the ON key. This will keep the calculator generating clock pulses, You may wish to write an endless loop routine in User Code to do the same. Use a logic probe or escilloscope to verify that there is a periodic reset pulse at U19-4, U1-15, and U3-15. The higher outputs

of the Tens Counter, U3-5,6,9,11, should remain low. You should also check that the MP-41 signals, Ø1, Ø2, SYNC, ISA, DATA, and VCC are there at the end of the MLDL cable assembly,

Section 4. The Data Input Shift Register. Recall that the DATA line is the contents of the HP-41 CFU's C register. U4, U5, U6, and U7 latch the serial bit stream at the phase which stops the least significant bit of the C register at pin seven of U7, DLO. The DATA STROBE signal is produced at U18-10. The 3-input AND gate is shown with the Control Signals Generator. You must wire U18 along with U4, U5, U6, and U7. Verify the wiring by running the calculator and checking for a periodic DATA STROBE. Enable the outputs of U4 thru U7 by temporarily wiring DATA ENABLE, high. Check that none of the outputs of U4 thru U7 are stuck high or low.

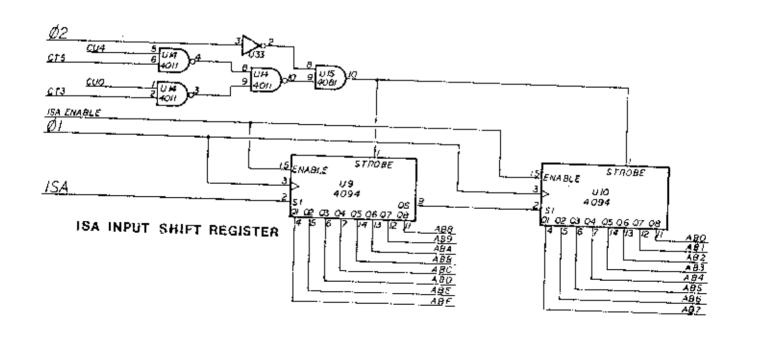

Section 5. The Isa Input Shift Register. U14 and U15 decode two atrobs pulses each machine cycle. One strobe pulse latches the instruction into U9 and U10. The next atrobs pulse latches the next instruction address into U9 and U10. Temporarily tie the ISA EMABLE high and verify periodic strobe pulses at U9-1 and U10-1. Also check that none of the U9 or U10 outputs are stuck high or low.

Section 6. The Control Signals Generator. Be very, very careful when wiring the control block. It is the heart of the MLDL. Mistakes here will be hard to find. U23 and U24 are comparator circuits which select the EPROW or ROME in response to the upper four Addross Bus lines, AB(C-F). U23 compares AB(C-P) with the upper helf of the address space of whatever port the MLDL is plugged into.

Port 1 = 9XXX Port 2 - BXXX Port 3 - DXXX Port 4 - FXXX

The output of D23 is used to select the EPROM. U24 compares AB(C-F) with the ROME address switches and selects the ROME whenever there is a match. You can map the ROME into any 4K block you wish. But watch out. 9locks D, 1, and 2 are used by the HP-41.

U20, U25, U15, and U13 decode and latch the WRITE S&X instruction. PRITE SEX is actually an HP-41 NOP, hex code 040. U20, U25, and U15 decode the instruction field from the Isa Input Shift Rogister and U13 latches the output, setting up the MLDL for a write to ROME sequence as described in UNDERSTANDING THE MLDL. U21 and U26 are used to decode certain of the highest sixteen addresses in the EPROM space. For example, the I/O port is at XFFF.

Connect the MLDL to Port 4 and press ON. The calculator should function since nothing more has been connected to the port signal lines. Verify that a sequence of periodic pulses are produced at U17-10 whenever ON is pressed. The EPROM output signal at U16-10, PROMO\*, should be a similar sequence of negative pulses. Set the ROME address switches to the lower half of Port 4, EXXX. (RA1, RA2, and RA3 should be high. RA0 should be low.) REN must be high to enable ROME output to the calculator. Verify that U17-6, RAMO\*, and U15-4, RAMCB\*, produce a sequence of negative pulses similar to PROMO\*. The RAM pulses will be a bit narrower if you are using a 'scope, since they are gated by Ø1.

Section 7. The Isa Output Shift Register, Ull and Ul2 comprise the Isa Output Shift Register. At phase forty-four the shift register is loaded with the data on the input lines, IoS(0-9). The data is shifted out to the HF-41 during the last ten phases of a machine cycle. U28 is the MLDL ISA line driver. The flip-flop, Ul3-2, only enables the MLDL cutput during the last ten phases of a machine cycle in which the SPKOM, ROME, or IMPUT PORT was addressed.

Wire the Isa Output Shift Register and Driver, but don't connect the output of the Driver, U28-11,13, to ISA. We are not yet ready to send things to the HP-41. Check that U13-2 pulses when ON is pressed. Ground the input pins to U11 and U12, IOS(0-9). Verify that no pulses are output at U12-3 while the calculator is running. The next verification steps take time, but they are worth it. Start with IOSO. Mire the input line high and verify a pulse out at U12-2. Rewire the input line low. Do the same test for IOS1 thru IOS9. Unwire IOS(0-9) from the ground. Connect U28-11,13 to ISA.

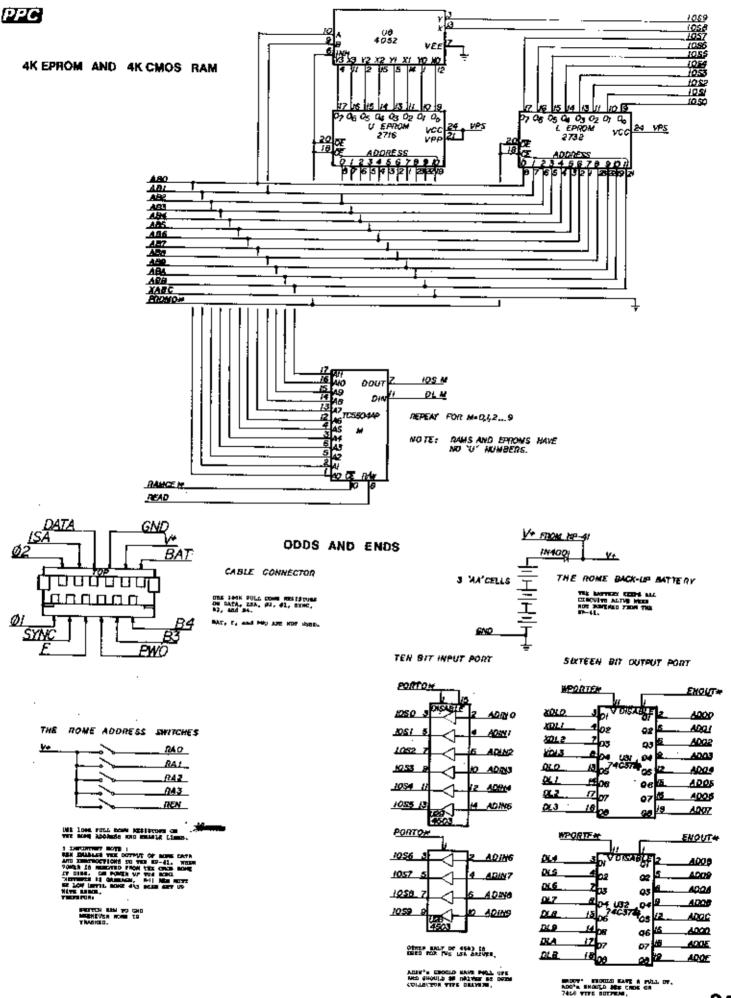

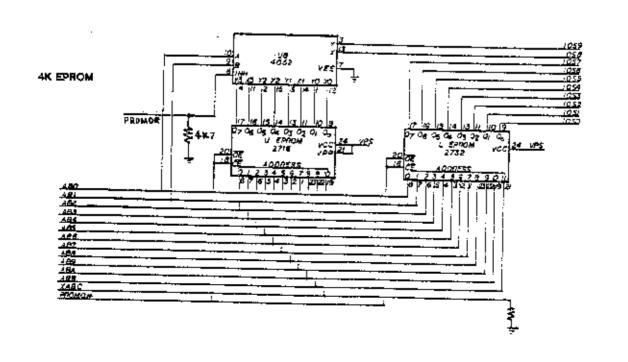

Section 8. The EPROM Array. The 2732 is the L EPROM

and the 2716 is the U BPROM. U8 18 a switch which directs the correct pair of U EPROM outputs to IOS(8, 9). The pair is selected by the lowest address lines, ADO and ABI. You will need to install EPROMs which contain women and a wall a catality 2. You should see a complete EPROM catalog. Assign xeam to a key. Use HN from the PPC ROM or the machine code CODE to transfer the alpha word PFFF000 to the X register. Key xerom and one pulse should be produced at U22-1, WPORT\*. If you wish to install U31 and U32 you can now write to the Output Port. Check that REN is low. Use the User Code routine WROME to write to the ROME. Verify that each xerom asserts RAMCE\* but not READ.

Section 9. The ROME. Install the 5504s with the MLDL disconnected from the HP-41 and the MLDL batteries removed. Install the MLDL batteries and connect up the HP-41. Check that the ROME address switches are still set for block E. Use the User Code routine ZROME to zero the ROME. ZROME isn't a fast routine. Enable the ROME output by switching REN high. Use VROME to view ROME contents. There should be nothing but zeroa. That's it. You're done.

Use WRUME and VROME to poke and peek around in the HP-41. Use WROME to load a PAT and abx or tas in ROME. Have fun, try some of your own M-Code!

#### 2 ROME

SORME fills sequential ROME words with zeros.

XEQ ZROME. The first prompt is START=? Enter the hex address of the first ROME word to be zeroed. The calculator is in the alpha mode. R/S. The second prompt is KND=? Enter the hex address of the last ROME word to be zeroed. R/S. Every ROME word from the start address to, and including, the end address will be zeroed.

A FFF size block takes about eight minutes on my HP-41.

Non HP functions used are x+Y, RXL, X>ROH, CODE.

| 01+Lb2 f2ROHE1 | :ê √L#             |

|----------------|--------------------|

| ez ÁDN         | L9 ARC: 01         |

| 93 1S7ART=11   | 28 CDDS            |

| ga PROMPT      | 21 RK              |

| es as"o ei     | 22 RML             |

| 86 *5ND=2*     | 23 RM.             |

| 97 PROMPT      | 24 E()Y            |

| 89 RDFF        | 25 599 L           |

| 89 COME        | 26 RDm             |

| lê "i"         | 27+ <b>55</b> , 91 |

| 11 COME        | 28 XXR6M           |

| 12 647         | 29 LASTX           |

| 13 304.        | 38 X+Y             |

| 14 100.        | 31 N#Y2            |

| 15 800.        | 32 CTO 81          |

| 16 -F888.      | 33 -30HE-          |

| 17 COME        | 34 TONE 9          |

|                | TS END             |

## VKOME and WROME

VROME displays the ROME contents. WROME displays the ROME contents and can change ROME contents.

XEQ VROME. The prompt is "ADDRESS?" Enter the first NOME address to be displayed. R/5. The RP-41 shows the address and the contents. R/S. The mext address and contents are shown. Step through the memory by pressing R/S. Select a new starting address by entering it into the alpha display. Step backwards through memory by setting flag 1 true.

XEQ WROME. The prompt is "ADDRESS?" Enter the first ROME address to be investigated. R/S. The HF-41 shows the address and contents. Pressing R/S will step through memory. Change the contents of a diaplayed memory word by entering the new contents into the alpha display, R/S. The address and the new contents will be diaplayed.

Non HP functions used are Y-x, QR, ROM>X, RXL, X>ROM, LODE, and DECODE.

| Bleist -Aboat.     | 20 ASHF                 | 40+LBL *#ROME* |

|--------------------|-------------------------|----------------|

| 82 ACH             | 21 ASTO DI              | 4! ACH         |

| 83 FATORE5571      | 22 XOY                  | 42 *ADBRESS:*  |

| 84 <b>FROHP</b> T  | 23 ROM/K                | 41 PROMPT      |

| 85*L6L 84          | 24 RCL L                | 44 CODE        |

| <b>€</b> 6 F92C 27 | 25 XC)Y                 | 45 ENTER!      |

| BY COBE            | 26 - 1 <b>0000000</b> 0 | 46 ENTER*      |

| MA FC? Bi          | 27 CDD8                 | 47+LBL 03      |

| an other:                   | 28 OR      | 49 XFQ 44  |

|-----------------------------|------------|------------|

| A 121                       | 29 DECODE  | 49 \$76F   |

| .: COD5                     | 36 45₩     | 58 4.76 28 |

| 12 Y-7                      | 31 R570 92 | 51 alu ea  |

| 13418(4)                    | 32         | 52 RJH     |

| IA EMIERI                   | 33 AMCL 9: | 52 RXL     |

| 15 ENTER+                   | St fr f    | 54 RXL     |

| 16 *L88# <del>67#28</del> # | SS ARCL BC | 56 RXL     |

| 17 CODE                     | JG REM     | 56 CDDE    |

| 28 OR                       | 37 AYJEW   | 57 OK      |

| 19 DEC 986                  | Ja RTH     | 58 XXAQ#   |

| -                           | 39 610 😝   | 59 RD₩     |

|                             |            | 68 G*6 93  |

|                             |            | 61.60      |

#### THE IC LIST

- CD4013 Dual D Flip-Flop

- U1, U1) CD-1017 Decoded Decimal Counter U2. U3

- CD4094 8-Bit Shift and Store Register

- V4, U5, U6, U7, U9, U10 CD4052 Differential 4-channel Multiplexer

- CD4021 8-stage Parallel Input Shift Register 011. 012

- CD4011 Quad 2-input NAND C14, U27 CD4081 Quad 2-input AND

- CD4021 Quad 2-input AND U15, U19 CD4021 Triple 3-input NAND U16, U17 CD4073 Triple 3-input AND

- U1B

- CD4078 8-input NOR/OR

- CD4068 8-input NAND/AND 021

- CD4012 Dual 4-input NAND [[22

- CD4063 4-bit Magnitude Comparator U23, U24

- CD4028 BCD-to-docimal Decoder

- U25. U26 CD4049 Hex Buffer/Inverter

- CD4503 3-state Hex Buffer

- U28, U29 74C373 8-bit Latch

- 031, 032

- TC5504AP-2 4Kx1 CMOS RAM 16

- MO, M1, M2, M3, M4, M5, M6, M7, M8, M9 2716 2Kx8 EPROM C KPROM \*

- 2732 4Kx8 EPROM

- L EPROM '

\*Puget Sound Programing sells a MLDL RPROM set. For \$25 you get ROM>X, X>ROM. CODE. DECODE, ROM>REG. REG>ROM and some more. Plus the documentation that tells what the routings do. Add \$5 for mailing outside of the U.S. and do. A CANADA.

## THE ROM ADDRESS SPACE

The \*PPC HP-41 Assembly Language Listings Number 2\* gives a short description of the HP-41 XROM organization. That information is repeated here. The addresses are given as four hex digits. For example, X000 represents the first address in any 4K block. In each 4K block above 5000, the only blocks allowed for XROMs, there are a number of preassigned address not used for instruction code. The following table lists the preassigned addresses and describes their use.

K000 The KROM number in hex. This is the first of the two numbers you see when viewing a programmed ROM function after the ROM module has been removed. For example, the function KROM 16,07 would come from a ROM with 010 stored at the

first address.

X001 The number of functions, in hex, which are displayed in a CATALOC 2.

X002 thro

X0t'T 000 LL= MM +2

The two coll words mark the end of the FAT.

Each entry in the FAT requires two words. There is a high-order word at the even numbered address and a low-order word at the odd numbered address, The high-order word contains the most significant byte of the functions starting address. The loworder word contains the least significant byte of the Functions starting address.

If the function is written in Machine Code the FAT address is the address of the first executable instruction, and bit nime of the high-order word is zero. If the ROM function is in T-Code, the FAT address points to the first byte of the desired USER label instruction, and bit nime of the high-order KAT WORM is one the high-order FAT word is one

In most ROMs the ROM name is the first function listed in the FAT. This is just a machine code function with one instruction, return. This is a simple trick to list a ROM name first in a CATALOG 2. There is no requirement for a ROM to have a name.

```

XOJJ thru

JJ= MM +3

```

XFF3 This is where the Machine Code goes.

XFFA These are the seven scanned entry points. Unless you know exactly what these addresses are for, set them to DDO. Otherwise the calculator will crash or be psychotic.

XYYB thru

XFFE These words are for the ROM revision number. space is available for the MLDL user. It will be useful to identify your own revisions!

XFFF This is the ROM check sum. It is used by the Diagnostic ROM to verify the contents of MP ROMs.

The address space between 3000 and 4PFF is available. It should only be used by the experienced Machine Code Dřogrammer.

#### A PAT EXAMPLE

The following is the Function Address Table from a hypothetical ROM or EFRON which contains the the "Useful M-Code Routines" and a User Code routine, rest. whose label is at X573. The XROM number is mineteen.

| X000 (         |             | The XROM number, 19.                |

|----------------|-------------|-------------------------------------|

| X001 0         |             | The number of functions in the PAT. |

| X002 (         | 100         | 1                                   |

| XDD3 (         | JEA .       | ROM>X                               |

| X004 (         | 000         | <b>;</b>                            |

| X005 0         | IFC         | XXADM                               |

| <b>XO</b> D6 0 | 701         |                                     |

| <b>X0</b> 07 ( | 102         | : X>A                               |

| XDO8 0         | 101         | <del>,</del>                        |

| X009 0         | 00C         | 1 T 5 5                             |

| XOOA 2         | 205         | 1                                   |

| KOOB (         | 173         | F"TEST"                             |

| X00C (         | 70 <b>0</b> | 1                                   |

| XOOD D         | 100         | The required nulls                  |

SOME USEFUL M-CODE ROUTINES

These routines were written by Faul Lind (6157). These routines were written by Faul Lind (614)

The addresses are for example only. The code is

position independent. Just don't cross any 4K

houndaries, Be sure to add the address of the first

executable instruction to the function table.

## ROMER

Given a 16 bit binary address in the lower 16 bits of X, RDM>X returns the 10 bit ROM word in X and the incremented address in L.

```

XQE5 098

(Routing name

x0Ee 03€

XOF 7

0.00

OOF

XOEB

012

X0F9

READ 3

Read the X register

XOEA DEG

RCR 11

⊁0EB

180

Rotate left 3 digits

XOEC 330

FETCH 56X

Get the ROM word

A=C ALL

Copy to A

XOED THE

XOEE

05A

Ç≖0 #

C=0 M5

:Clear address register

XGEF

♦5E

(Copy the instruction to X

xoFo oێ

MP1TE 3

XOF1 CAE

ACSC ALL

;Clear the instruction

|Increment the address

|Rotate the address to 4 LSDs

C=0 S&X

X0F2 046

C=C+1 M

X0F3 23A

X0F4 03C

HCR 3

WRITE 4

/Write the address to L

XOF5

XOME SED HIN

rReturn

```

## **X>ROH**

Given a 16 bit address followed by a 12 bit. word in the lowest bits of the X register, x>RGM will write the lowest 10 bits (The M-Code) to the ROME address, Address portion is not

```

altered. I does not contain the incremented

address.

:Routine hame

XOE7 GAD

коғы фағ

хогя

012

R

XOFA G3E

018

Kare

READ 3 Read the X register white 56% :040 is the MDDL write Arm :Return

XOFC OFB

KOPD

3E.D

Append character code in X to the loft of

the alpha register.

:Routine name

XOFF 081

x:00 03E

A101 018

Read the X register

3.102 OFB

READ 3

'RCDBIN' is a mative routine'

Pag (Set pointer to zero

Gec aR, + (Low byte of C into G

7NC GO (Append character)

Convert to binary BCDBIN

X103 380

008

X1:34

XLDS

056

X106

Append character in G to

salpha register. APPEND is

a native routine.

051

L GU

X 5 0 7

086

XIOS

(Returns through APPEND

* A netive routing is a routing which is

built into the HP-41.

Toggle flag 55 to dispble the printer,

:Routine name

OB5

2100

XIOA

X10E

014

7FSET 0

380

```

## THE EPROM YORMAT

01F

388 013

384

388

348

JC +3 SETF

JNC +2

CLRF 0

C=ST X

PIN

READ 14

XLDO

XIOF

XIOF

×110

X111

X113

X114

The types of EPROMs used in the MLDL and other EPROM boxes are all eight bit word formats. The HP-41 uses a ten bit ROM word format. The MLDL uses one EPROM, the L EPROM, for the lower eight bits of the ROM word. The least significant bit of the L EPROM is the least significant bit of the ROM word. The upper two bits of the ROM word are stored in the U EPROM. Each word in the U EPROM stores the upper two bits for four consecutive ROM words. The bits are paired as indicated in the example calculation below. The following EPROM MAP is for the M-Code routine TSS.

| 10 837                                              | N/M MCAN                                | 1901                                                                                                             | 1                                             |

|-----------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 1389, 1768<br>U C PROS<br>OT C4 D0 29, 24, 24 C4 A0 | 1                                       | d   x)of<br>c   xioa<br>c   xioa<br>n   xioc<br>i i   xioc<br>i i   xioc<br>c   xioc<br>i i   xioc<br>i i   xioc | 565<br>036<br>014<br>360<br>017<br>349<br>013 |

| 100 T T T T T T T T T T T T T T T T T T             | 1 1 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0 0 E110<br>0 0 E111<br>0 0 E117<br>0 0 X13<br>0 0 X13                                                           | 370 1                                         |

The next example shows how to calculate the U EPROW address and position for a given ROM word address.

write the RDM word address out in binary. X109 becomes

XXXX000100001001,

Shift the address right by two bits,

XXXX0001000010.01

The value to the left of the binary point is the U EPROM address and the value to the right of the point is the U EPROM pair number,

.00 is pair 01, 05 .01 is pair 03, 02 .10 is pair 05, 04 .11 is pair 07, 06

The ROM word at address X100 is stored in the L MPROM address X100 and the C EPROM address 042 outputs 03, and 02.

Lynn A. Welkins (7344 1912–17) Place NE Redmond, WA 98052

See pages 32 thru 34 for schematics.

folks at HP know!

BLOCK DIAGRAM SHOWING DATA AND CONTROL PATHS, ØI, Ø2,AND PHASE COUNTS CT, CU, ARE NOT SHOWN.

## MACHINE LANGUAGE DEVELOPMENT LAB.