# HP-75 PORTABLE COMPUTER

# SERVICE MANUAL

HP**-**75

Portable Computer

SERVICE MANUAL

#### Section

Page

# I GENERAL INFORMATION

| 1-1.  | Introduction        | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1-1 |

|-------|---------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| 1-7.  | Product Description | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1-2 |

| 1-10. | Identification      | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1-4 |

# II THEORY OF OPERATION

| 2-1.           | Functional Description                           |

|----------------|--------------------------------------------------|

| 2-8.           | CPU                                              |

| 2-13.          | RAM                                              |

| 2-17.          | MAR                                              |

| 2-19.          | Buffer                                           |

| 2-21.          | ROM                                              |

| 2-24.          | LCD Display                                      |

| 2-27.          | Display Controller                               |

| 2-29.          | Display Driver                                   |

| 2-31.          | Card Reader                                      |

| 2-35.          | Clock/Keyboard/RTC                               |

| 2-40.          | Keyboard                                         |

| 2-43.          | HP-IL IC                                         |

| 2 <b>-</b> 51. | Power Supply                                     |

| 2 <b>-</b> 55. | Card Reader Description                          |

| 2 <b>-</b> 57. | Magnetic Card                                    |

| 2-60.          | Card Reader IC Electronics                       |

| 2-62.          | System Bus Communication                         |

| 2-71.          | Analog Circuitry                                 |

| 2-73.          | Input/Variable Gain Stage                        |

| 2-75.          | Bandpass/Fixed Gain/Offset Correcting Stage 2-22 |

| 2-77.          | Schmitt Trigger                                  |

| 2-79.          | Inverter                                         |

| 2-81.          | Peak Detector                                    |

| 2-85.          | Automatic Gain Control                           |

Section

| 2-88.          | Noise Filtering                   | 24  |

|----------------|-----------------------------------|-----|

| 2-90.          | Bias Set                          | 25  |

| 2 <b>-</b> 92. | Tracking Adjustment               | 25  |

| 2-94.          | Write Amplifier                   | 25  |

| 2-96.          | Power Supply Description          | -25 |

| 2-97.          | DC-to-DC Converter                | 25  |

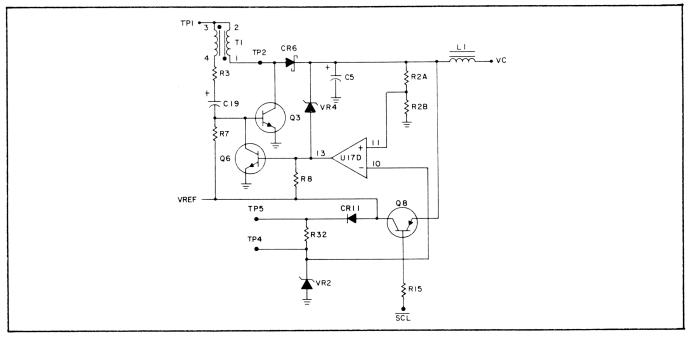

| 2-104.         | Battery Level Detect              | 27  |

| 2-106.         | Alkaline/Nicad Detect             | 27  |

| 2-110.         | Battery Charging                  | 27  |

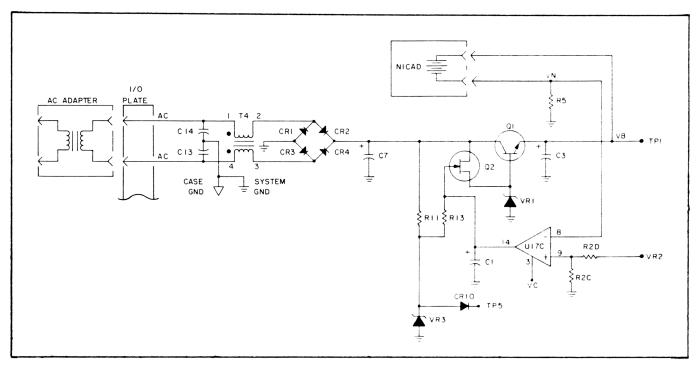

| 2-115.         | AC Operation                      | -29 |

| 2-117.         |                                   |     |

| 2-121.         |                                   |     |

| 2-124.         |                                   |     |

| 2-126.         | AC ESD/EMI Protection             | 31  |

| 2-129.         | System Timing                     | 32  |

| 2-132.         | Deep Sleep with POR Low           | 32  |

| 2-135.         |                                   |     |

| 2-138.         |                                   |     |

| 2-141.         |                                   |     |

| 2-144.         |                                   |     |

| 2-146.         |                                   |     |

| 2-149.         |                                   |     |

| 2-151.         |                                   |     |

| 2-153.         | Indirect Address Loading          | -39 |

| 2-155.         | Halt/DMA (Direct Memory Access)   | .39 |

| 2-158.         | Interrupt Structure               | .40 |

| 2-162.         | Power On Sequence                 | .41 |

| 2-166.         | Test                              | .43 |

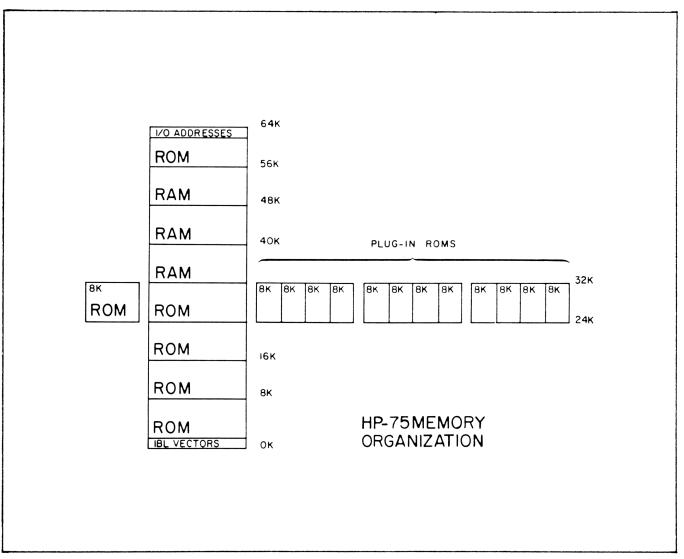

| 2-168.         | HP-75 Memory Organization         | .44 |

| 2-170.         | ROM and ROM Plug-ins              | .45 |

| 2-172.         | RAM and 8k Plug-in                | 46  |

| 2-174.         | I/O Space                         | .46 |

| 2-176.         | HP-75 System Software Description | 48  |

| 2-178.         | Power On                          | 48  |

| 2-180.         |                                   | .48 |

| 2-184.         |                                   |     |

| 2-186.         | Waiting for a Key                 | ·51 |

| 2-189.         |                                   |     |

#### Section

# Page

# III DISASSEMBLY AND REASSEMBLY

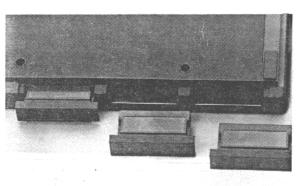

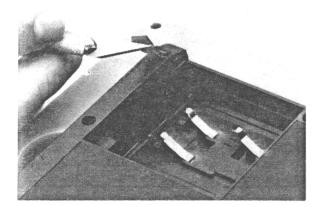

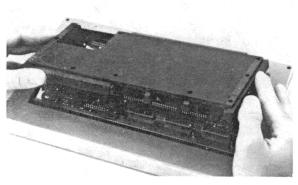

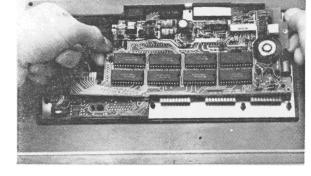

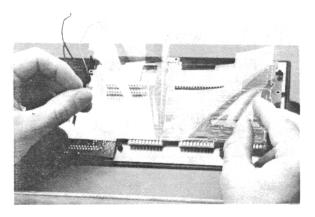

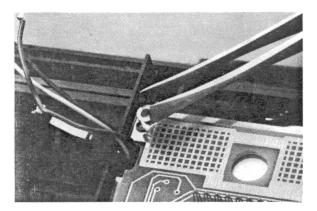

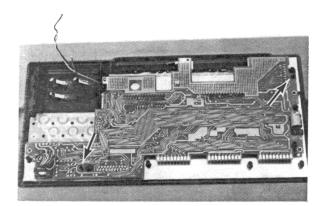

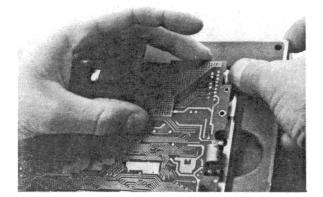

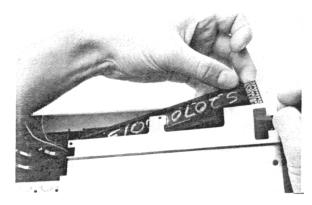

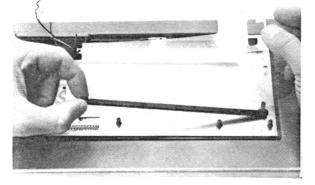

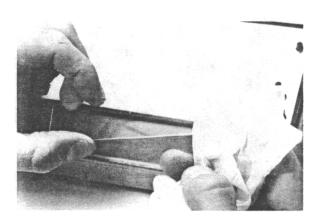

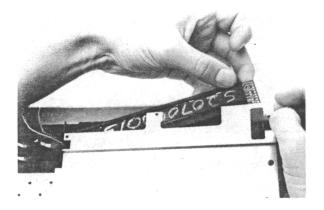

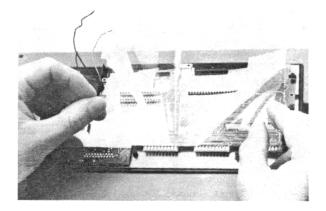

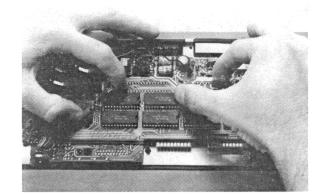

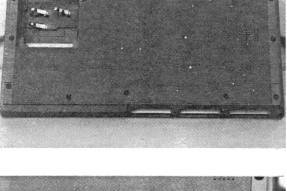

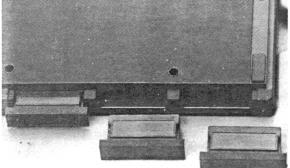

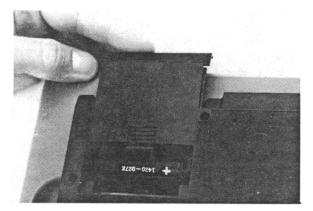

| 3-1.<br>3-4.<br>3-8.<br>3-9.<br>3-10.<br>3-11.<br>3-12. | Removing and Tightening Screws3Removing the Back Case3Removing the Power Supply/RAM PCA3Removing the Logic and Display Assemblies3Assembling the Logic and Display Assemblies3 | -6<br>-7 |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3-13.                                                   |                                                                                                                                                                                |          |

| IV                                                      | DIAGNOSTIC ROM                                                                                                                                                                 |          |

| 4-1.                                                    |                                                                                                                                                                                | -1       |

| 4-4.                                                    |                                                                                                                                                                                | -1       |

| 4-11.                                                   |                                                                                                                                                                                | -2       |

| 4-14.                                                   |                                                                                                                                                                                | -3       |

| 4-17.                                                   |                                                                                                                                                                                | -3       |

| 4-26.                                                   |                                                                                                                                                                                | -5       |

| 4-30.                                                   |                                                                                                                                                                                | -5       |

| 4-32.                                                   |                                                                                                                                                                                | -6       |

| 4-35.                                                   |                                                                                                                                                                                | -6       |

| 4-39.                                                   |                                                                                                                                                                                | -6       |

| 4-43.                                                   | Keyboard Test                                                                                                                                                                  | -7       |

| 4-51.                                                   | Clock Test                                                                                                                                                                     | -8       |

| 4-56.                                                   | Deep Sleep Test                                                                                                                                                                | -8       |

| 4-61.                                                   |                                                                                                                                                                                |          |

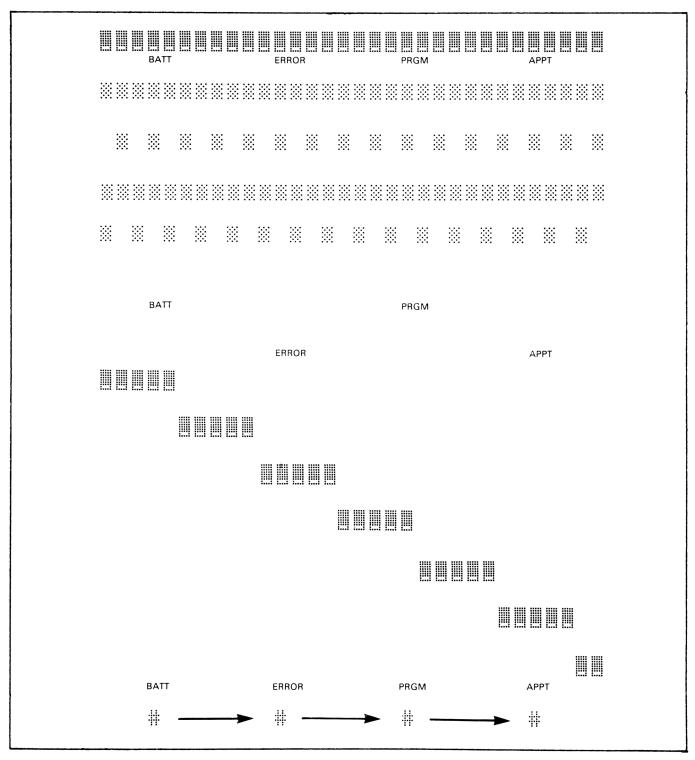

| 4-65.                                                   | LCD Driver Test                                                                                                                                                                | -9       |

| 4-69.                                                   |                                                                                                                                                                                |          |

| 4-73.                                                   | HP-IL Test                                                                                                                                                                     | 12       |

| 4-82.                                                   |                                                                                                                                                                                |          |

| 4-86.                                                   |                                                                                                                                                                                |          |

| 4-90.                                                   |                                                                                                                                                                                |          |

| 4-94.                                                   | Light Sleep Tests                                                                                                                                                              | 14       |

| V                                                       | TROUBLESHOOTING AND TESTING                                                                                                                                                    |          |

| 5-1. | Introduction        | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 5-1 | l |

|------|---------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|---|

| 5-7. | Initial Preparation | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 5-3 | 3 |

| Secti                | Page Page Page Page Page Page Page Page | зe  |

|----------------------|-----------------------------------------|-----|

| VI                   | ACCESSORIES                             |     |

| 6-1.<br>6-3.<br>6-7. | Introduction                            | - 1 |

| VII                  | REPLACEABLE PARTS                       |     |

| 7-1.<br>7-4.         | Introduction                            |     |

| VIII                 | REFERENCE DIAGRAMS                      | -1  |

## Illustrations

| Figure | Title                          | :   |   |   |     |   |   |   |   |   |   |   |   |   | Page          |

|--------|--------------------------------|-----|---|---|-----|---|---|---|---|---|---|---|---|---|---------------|

| 2-1.   | HP-75 System Block Diagram     | • • | • | • |     | • | • | • |   | • | • | • | • | • | 2 <b>-</b> 2  |

| 2-2.   | CPU Block Diagram              | • • | • | • |     | • | • | • |   | • | • | • |   | • | 2-4           |

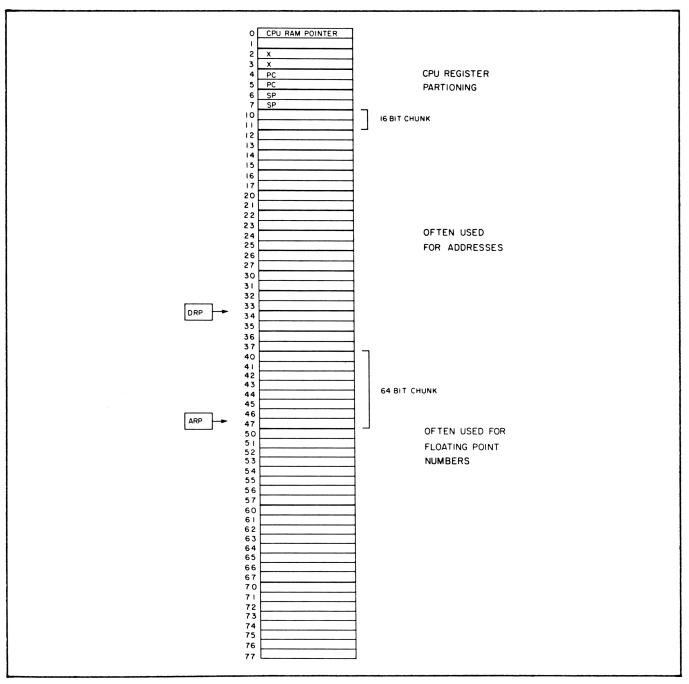

| 2-3.   | CPU Register Diagram           |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

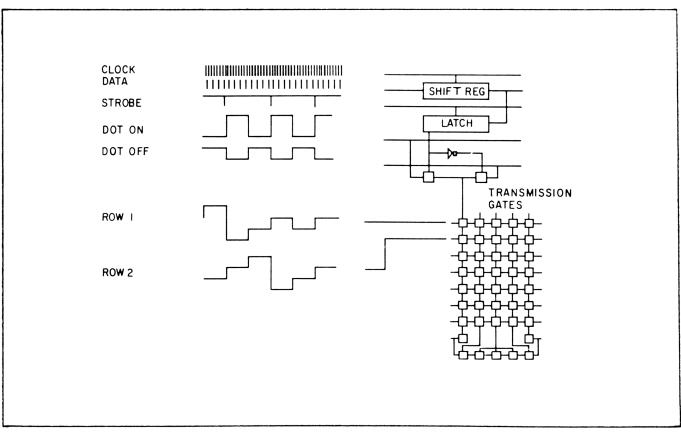

| 2-4.   | Display Waveforms              |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

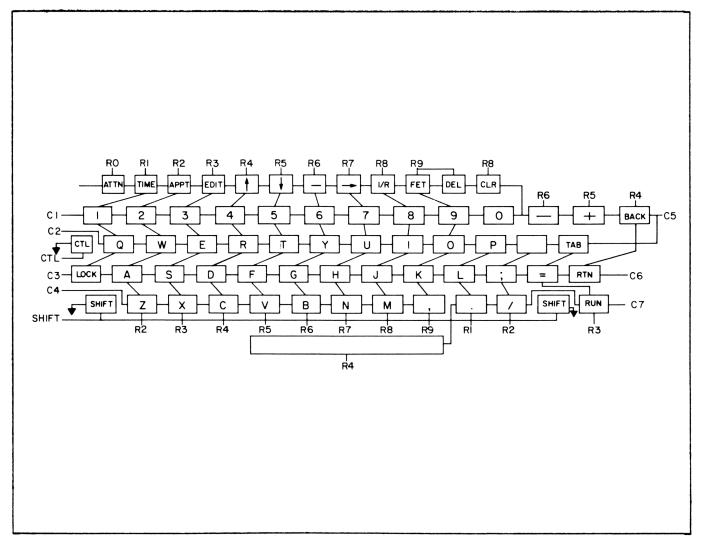

| 2-5.   | Keyboard Layout Diagram        |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

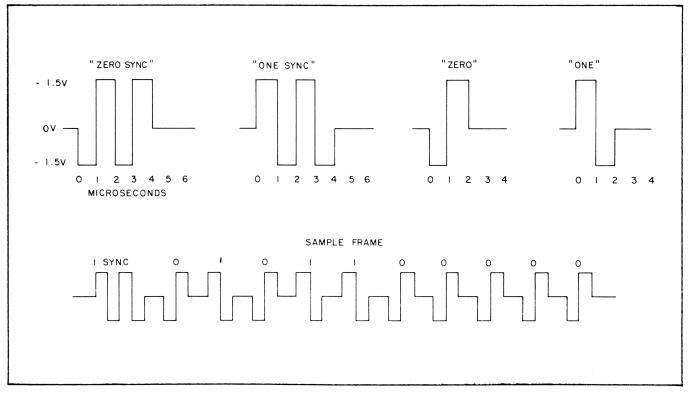

| 2-6.   | HP-IL Bit Encoding             |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

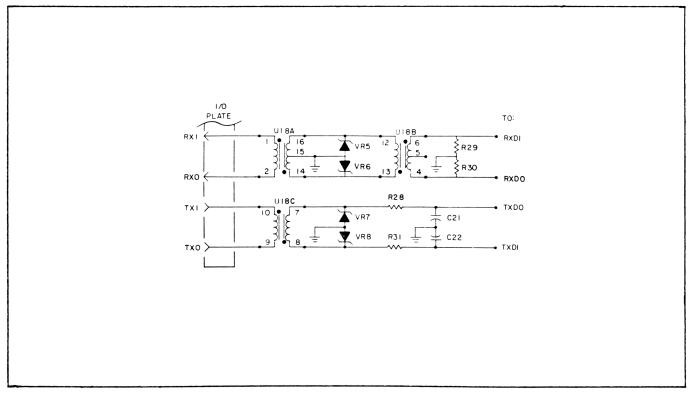

| 2-7.   | HP-IL Circuit                  |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

| 2-8.   | Magnetic card Layout           |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

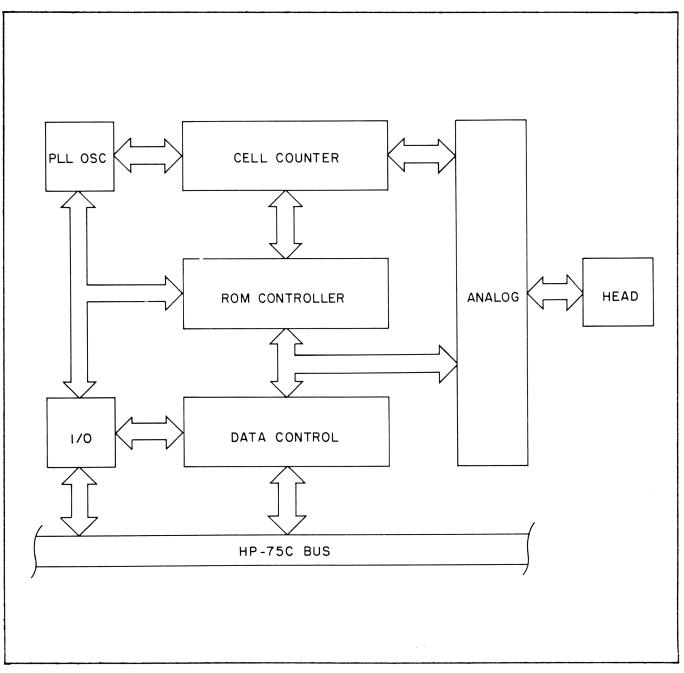

| 2-9.   | Card Reader Block Diagram      |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

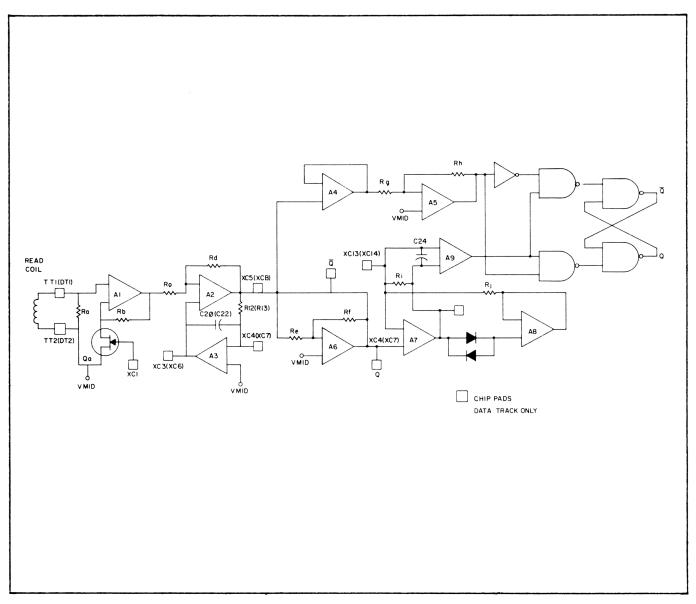

| 2-10.  | Read Sense Amplifier Diagram   |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

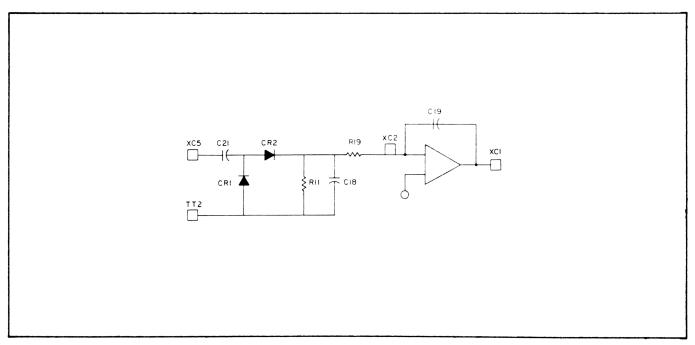

| 2-11.  | Automatic Gain Control Diagram |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

| 2-12.  | DC-to-DC Converter Circuit     |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

| 2-13.  | Battery Charging Circuit       |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

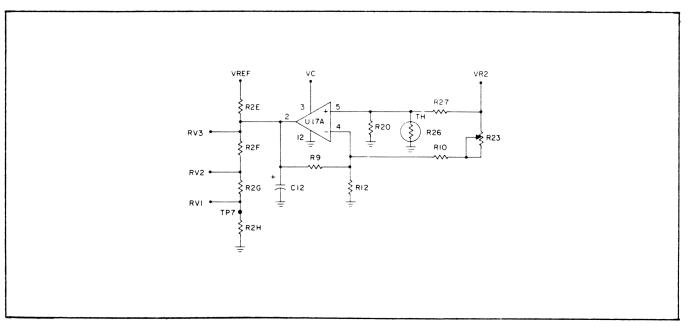

| 2-14.  | Display Reference Circuit      |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

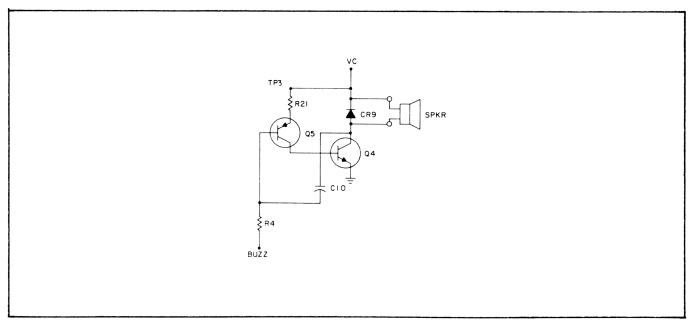

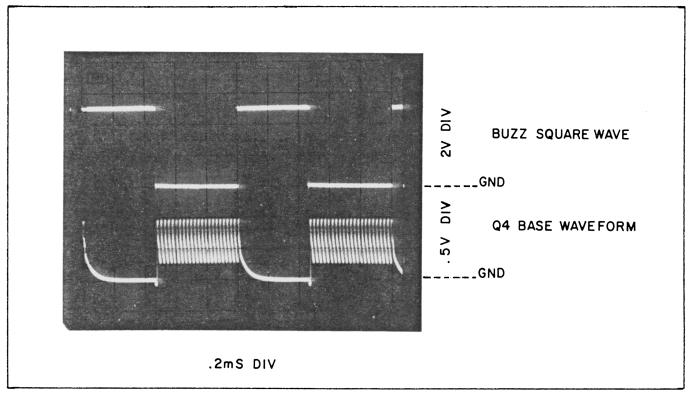

| 2-14.  | Buzz Circuit                   |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

| 2-15.  |                                |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

|        | Buzz Circuit Waveform          |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

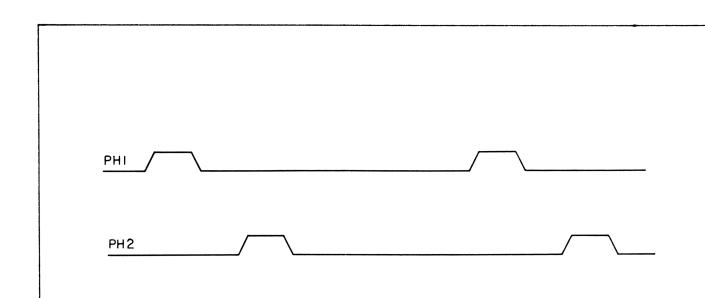

| 2-17.  | PH1 and PH2 Awake Timing       |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

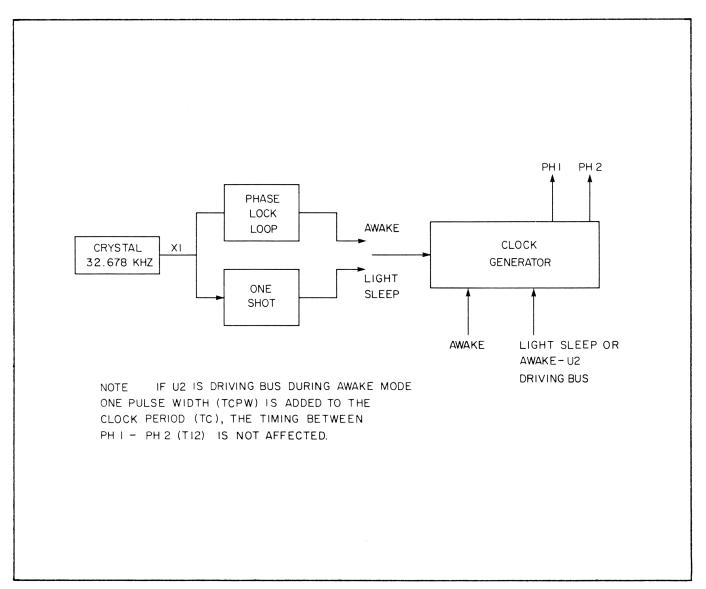

| 2-18.  | Clock Control Block Diagram    |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

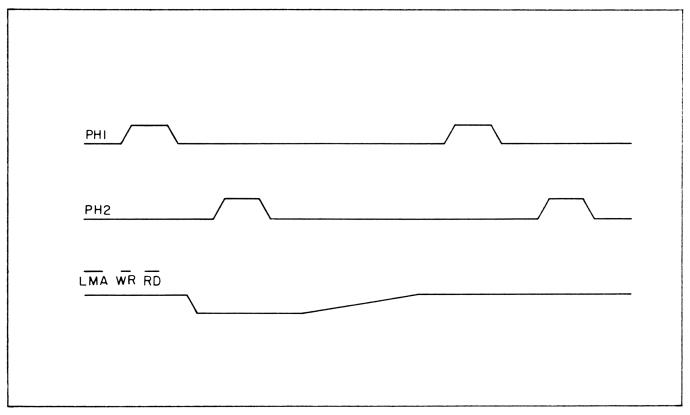

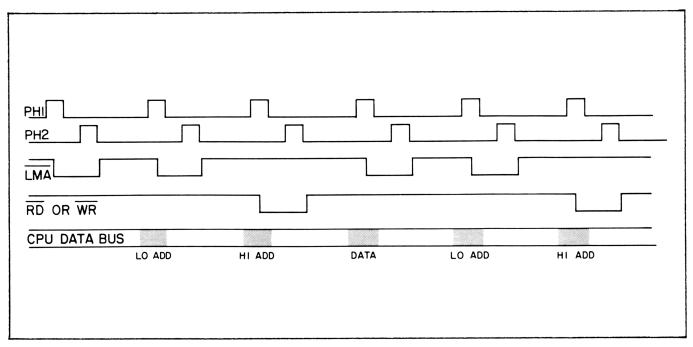

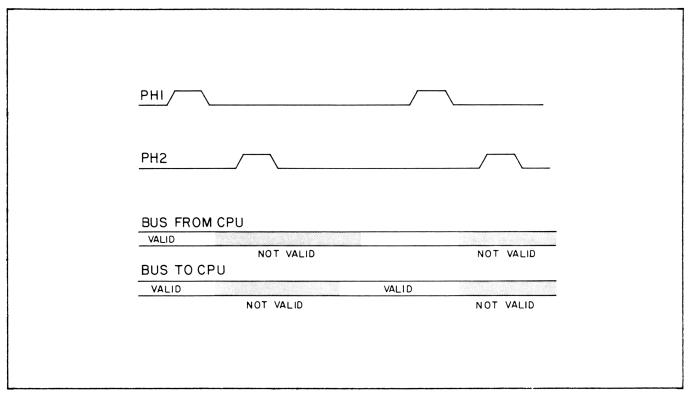

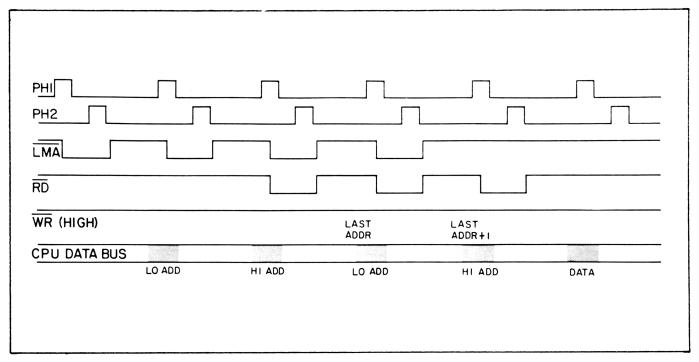

| 2-19.  | Control Line Timing            | • • | • | • | ••• | • | • | • | • | • | • | • | • | • | 2 <b>-</b> 37 |

| 2-20.  | LMA Direct Address Timing      |     |   | • |     | • | • | • |   | • | • | • | • | • | 2-38          |

| 2-21.  | Data Read/Write Timing         |     |   |   |     |   |   |   |   |   |   |   |   |   |               |

Illustrations

| Figure         | Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | age                 |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 2 <b>-</b> 22. | Indirect Address Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                  |

| 2-23.          | Priority Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .41                 |

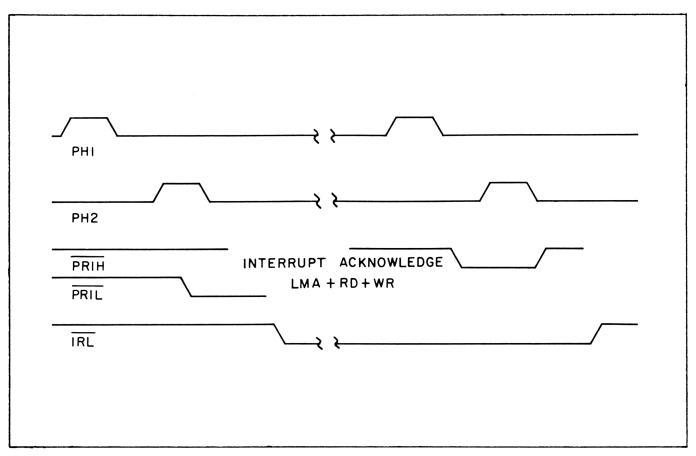

| 2-24.          | Interrupt Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42                  |

| 2-25.          | Power On Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |

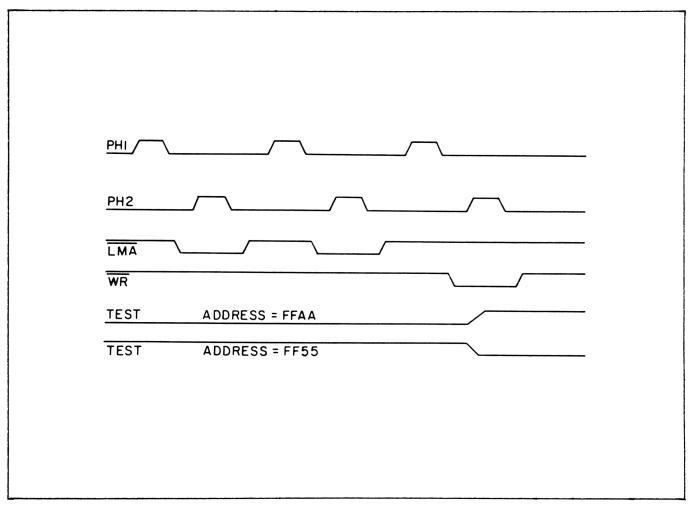

| 2-26.          | TEST Line Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |

| 2-27.          | Memory Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |

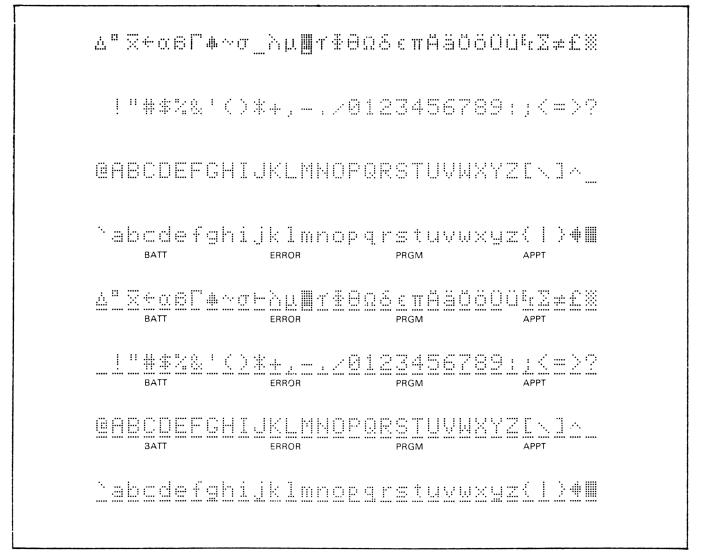

| 4-1.           | LCD Driver Characters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |

| 4-2.           | LCD Controller Characters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |

| 6-1.           | HP 82001B Battery Pack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

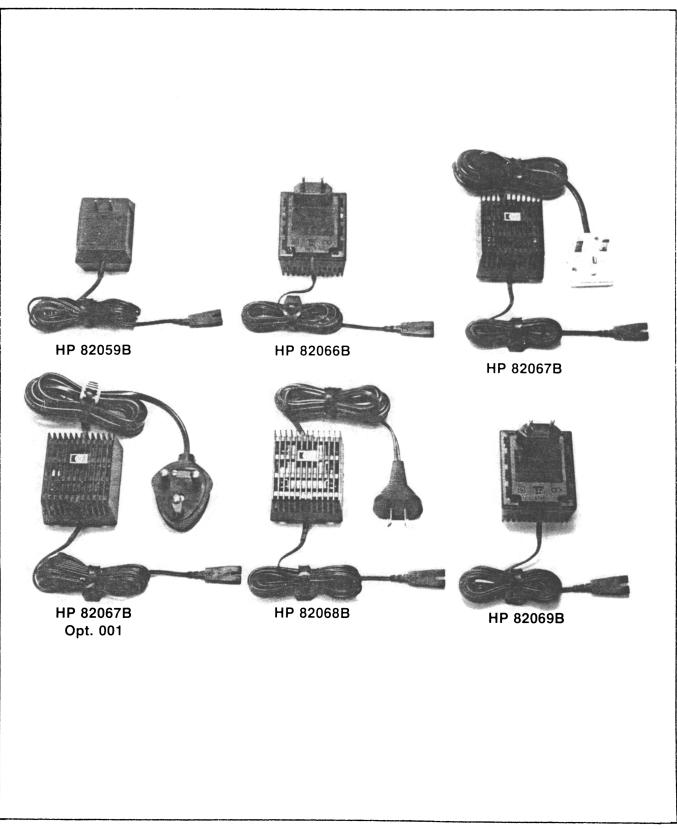

| 6-2.           | Rechargers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |

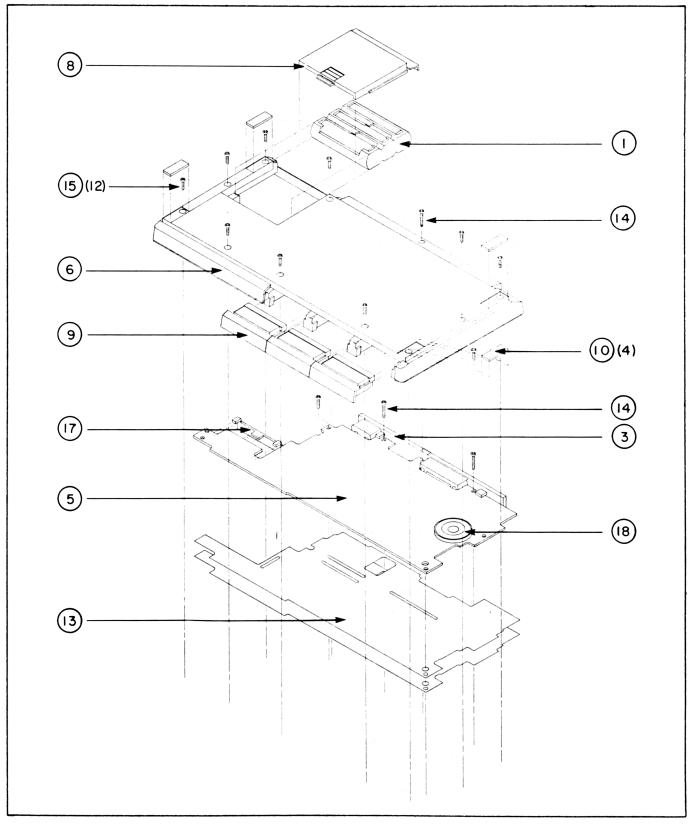

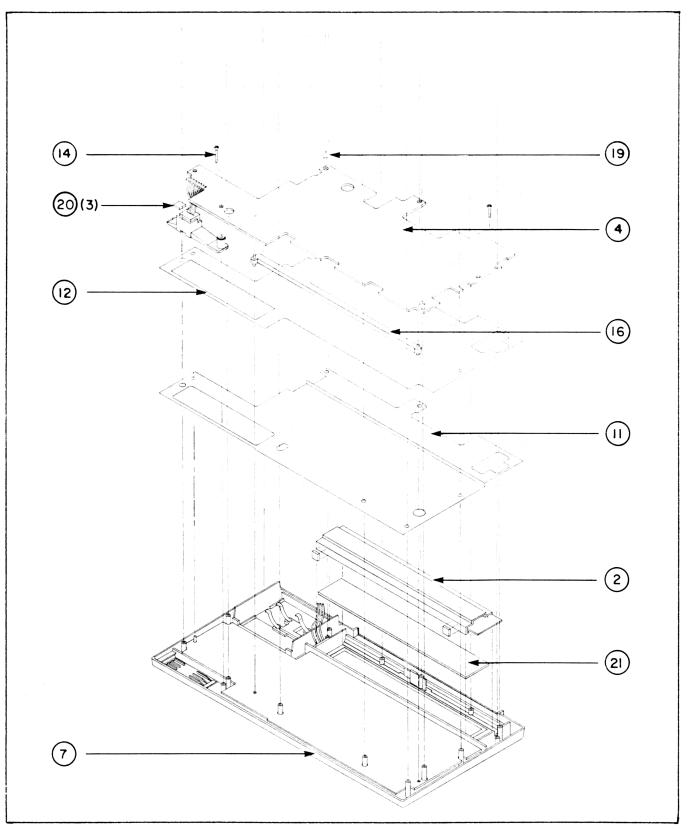

| 7-1.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -2                  |

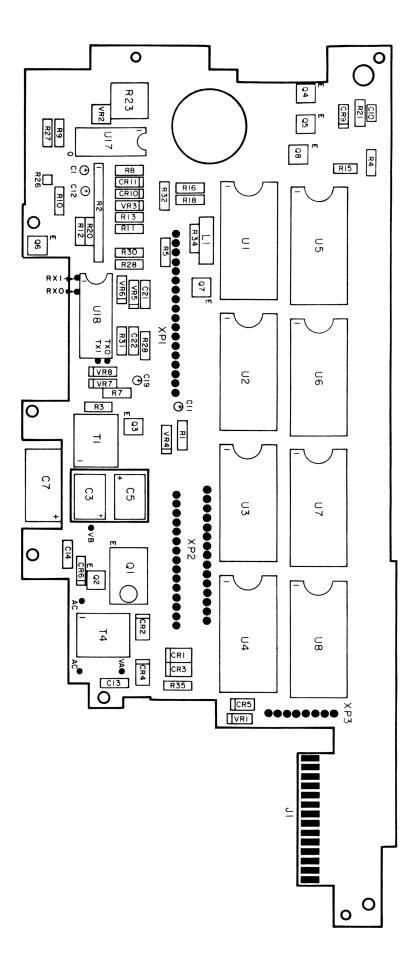

| 8-1.           | m () for our compared in provide the contract of the contract | 3-3                 |

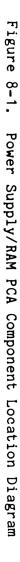

| 8-2.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-3                 |

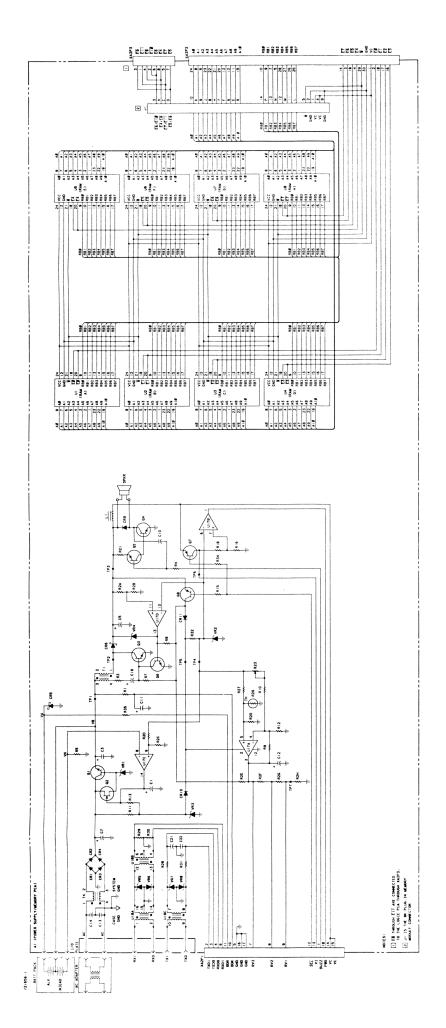

| 8-3.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | , j<br>3 <b>-</b> 5 |

| - 0 -          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3 <b>-</b> 5        |

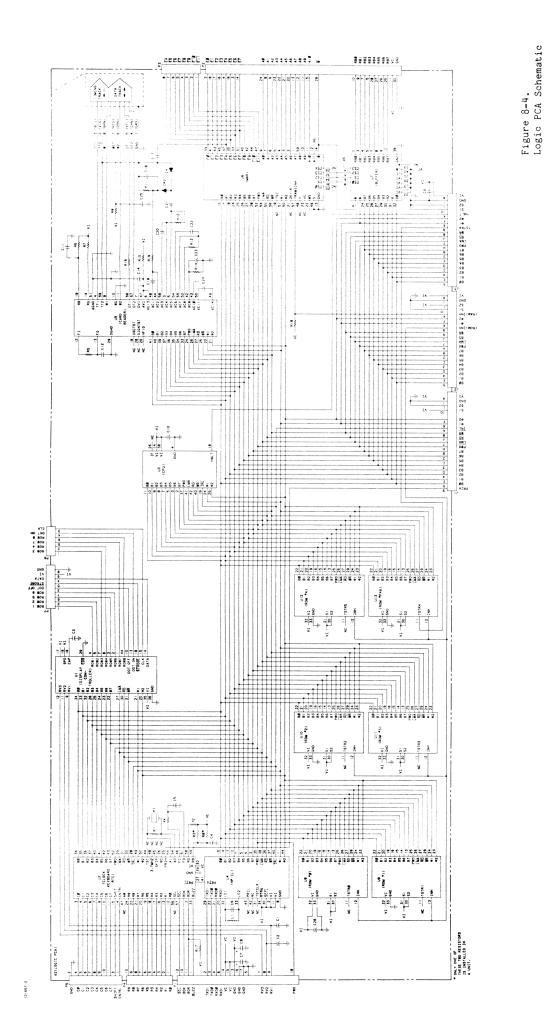

| 8-4.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |

| 8-5.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-7                 |

| 8-6.           | Display PCA Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-9                 |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |

# Tables

| Table | Title                                     | Page |

|-------|-------------------------------------------|------|

| 1-1.  | Specifications                            | 1-2  |

| 2-1.  | Signal Descriptions                       | 2-7  |

| 2-2.  | CPU Control Signals                       | 2-36 |

| 2-3.  | I/O Addresses                             |      |

| 3-1.  | Recomended Tools                          |      |

| 4-1.  | Key Reassignments                         |      |

| 5-1.  | Recommended Tools                         |      |

| 5-2.  | Repair Procedures                         |      |

| 5-3.  | Operational Verification                  |      |

| 5-4.  | Diagnostic ROM Error Messages             |      |

| 5-5.  | "Test" Program Listing                    |      |

| 5-6.  | "Verify" Program Listing                  |      |

| 6-1.  | Battery Troubleshooting                   |      |

| 6-2.  | Rechargers                                |      |

| 6-3.  | Recharger Troubleshooting                 |      |

| 7-1.  | HP-75 Portable Computer Replaceable Parts |      |

#### 1-1. INTRODUCTION

1-2. This service manual contains information to help you troubleshoot and repair the HP-75C Portable Computer.

Note: This manual will use HP-75 to designate the HP-75C.

1-3. This section describes the HP-75 and outlines how to use this manual.

1-4. The remainder of this manual is divided into 7 sections:

o A description of the HP-75 and how it operates (section II).

o Assembly/disassembly procedures (section III).

o A description of the diagnostic ROM (section IV).

o Troubleshooting procedures (section V).

o Accessories (Section VI).

o Lists of replaceable parts (section VII).

o Reference diagrams (section VIII).

1-5. Before using this manual in actual repair, read through sections I and II to become familiar with the HP-75 and its operation. Then read sections III through V to become familiar with the repair proceedures.

1-6. Additional information related to service is included in the HP-75 Owner's Manual:

o Section 8, Card Reader Operations, detail the use of the card reader.

- Appendix A lists the power cords and other accessories used with the HP-75.

- Appendix B explains the use and installation of the plug-in ROM modules and the memory module.

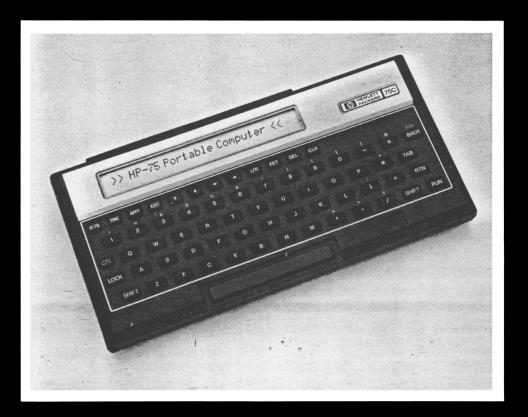

- 1-7. PRODUCT DESCRIPTION

- 1-8. The HP-75 Portable Computer is an integrated system which features:

- o Three operating modes:

- Edit mode consisting of both enhanced ANSI BASIC programming language and text writing.

- Time mode.

- Appointment mode.

- o 16K read/write memory, expandable to 24K.

- o Battery-powered circuitry.

- o CMOS circuitry for low power consumption.

- o HP-IL for general I/O operations.

- o Built-in magnetic card reader/writer.

- o Typewriter keyboard and editing keys.

- o 32-character LCD display.

- 1-9. Specifications for the HP-75 are listed in table 1-1.

#### Table 1-1. Specifications

Physical Properties

o Width: 25.7 centimeters (10.11 inches).

o Depth: 12.9 centimeters (5.09 inches).

o Height: 3.0 centimeters (1.17 inches).

o Weight: 680 grams (1.50 pounds).

Table 1-1. Specifications (Continued)

```

Environmental Limits

o Operating Temperature: 0 to 45 degrees C (32 to 113 degrees F).

o Charging Temperature: 10 to 40 degrees C (50 to 104 degrees F).

o Storage Temperature: -40 to 55 degrees C (-40 to 131 degrees F).

o Operating and Storage Humidity: 0 to 90 percent relative humidity.

Power

o Primary: HP 82001B battery Pack.

o Recharging time for pack: 9 hours.

o Usage: On (Awake)

200 milliwatts

Idle (light sleep) 100 milliwatts

Off (deep sleep) 200 microwatts

Display

o Type: LCD (liquid crystal display).

o Number of characters: 32.

o 5 \times 9 apparent dot matrix.

Keyboard

o 65 key QWERTY typewriter style.

o Consists of three groups:

- Typewriter Keys.

- Edit keys.

- System keys.

Interface

o Type: HP-IL (Hewlett-Packard Interface Loop).

o Default on Power Up: system controller.

Magnetic Card

o Length: 25.4 centimenters (10 inches).

o Width: 1.0 centimeter (0.38 inches).

o Thickness: 0.2 centimeters (0.09 inches).

o Temperature Limits: 4 to 32 degrees C (40 to 90 degrees F).

o Humidity Limits: 20 to 80 percent relative humidity.

```

Table 1-1. Specifications (Continued)

Card Reader

o Maximum read/write speed: 76.2 centimeters (30 inches) per second.

o Minimum read/write speed: 12.7 centimeters (5 inches) per second.

o Number of tracks: 2 data and 2 timing.

o density: 315 bits per centimeter (800 bits per inch).

o Format: 8 bits per byte.

o Formatted capacity: 650 data bytes per track.

o Encoding method: MFM (modified frequency modulation).

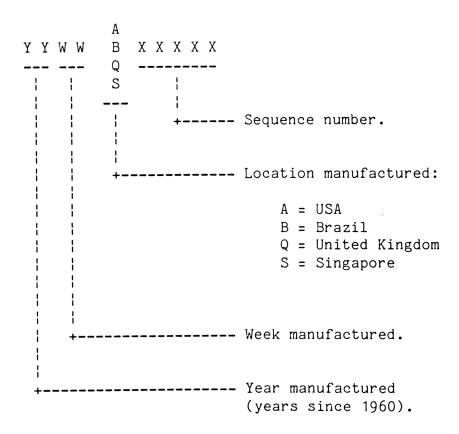

1-10. IDENTIFICATION.

1-11. The serial number of the computer is used for identification and determination of the warranty status. It is located along the top edge of the back cover near the battery door. Its format is shown below:

#### 2-1. FUNCTIONAL DESCRIPTION

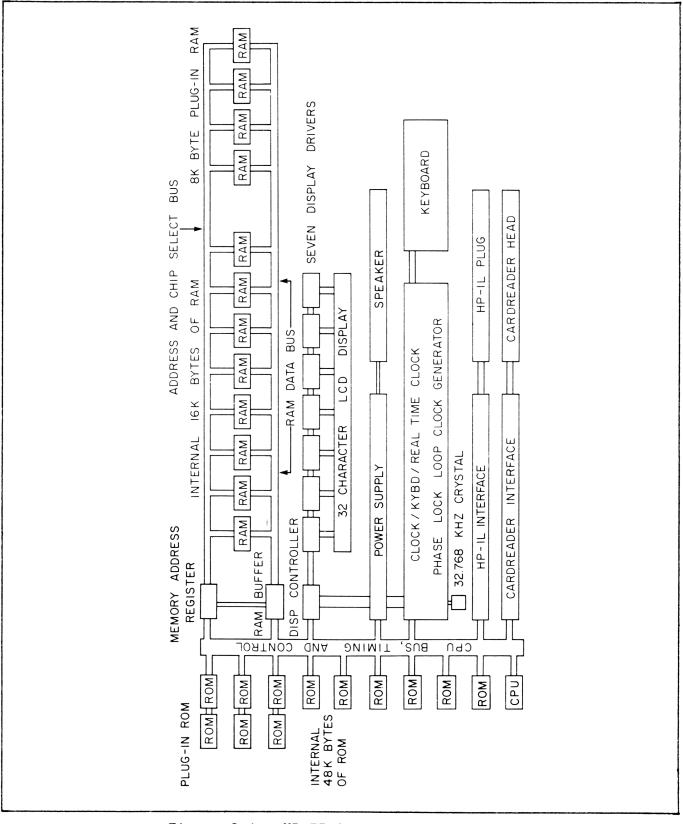

2-2. The HP-75 Portable Computer (see figure 2-1) consists of eight primary logic circuits:

- o CPU (central processing unit).

- o Clock/Keyboard/RTC (real-time clock).

- o RAM (random-access memory).

- o ROM (read-only memory).

- o LCD (liquid-crystal display).

- o Card Reader.

- o HP-IL (Hewlett-Packard Interface Loop).

- o Power supply.

2-3. The HP-75 provides several methods for the user to transfer information to and from the computer. Standard input entry is through a 65-key modified typewriter keyboard. Standard output is through the 32-character LCD display. The remaining I/O consists of:

- o 8K, 16K, 24K, 32K, 40K, or 48K plug-in RAM or ROM modules (BASIC or assembly files) up to a total of 144K.

- o Programmable 1 Hz to 1.7 kHz audio speaker.

- Hand-operated card reader providing both input and output capability. There are two tracks per card with a maximum of 650 bytes per track.

- o HP-IL interfacing, which allows up to 30 input and/or output devices on the loop.

2-4. Additionally, the HP-75 is able to expand its random-access memory using a plug-in 8k byte memory module.

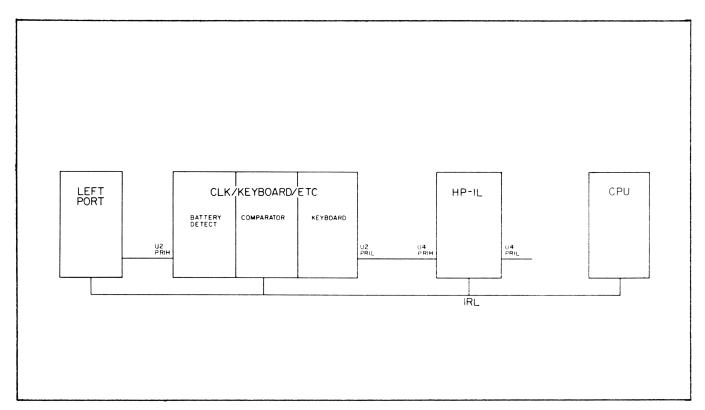

Figure 2-1. HP-75 System Block Diagram

#### Theory of Operation

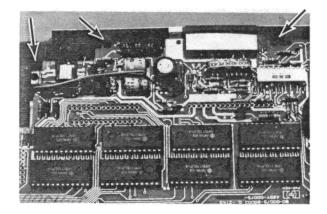

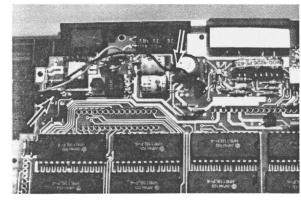

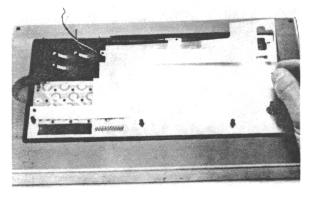

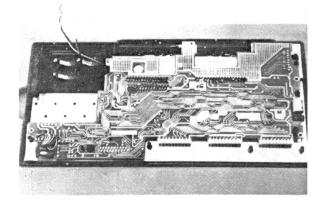

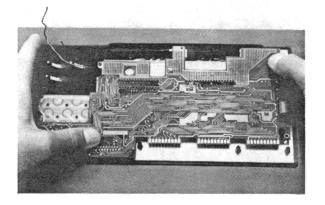

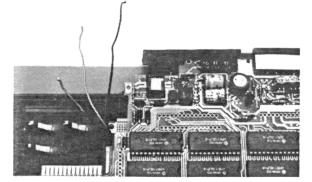

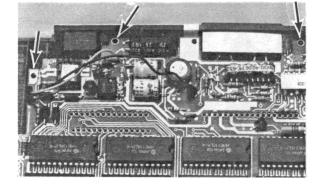

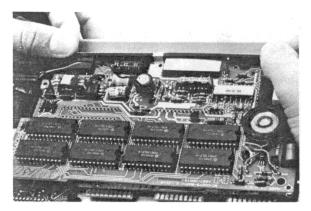

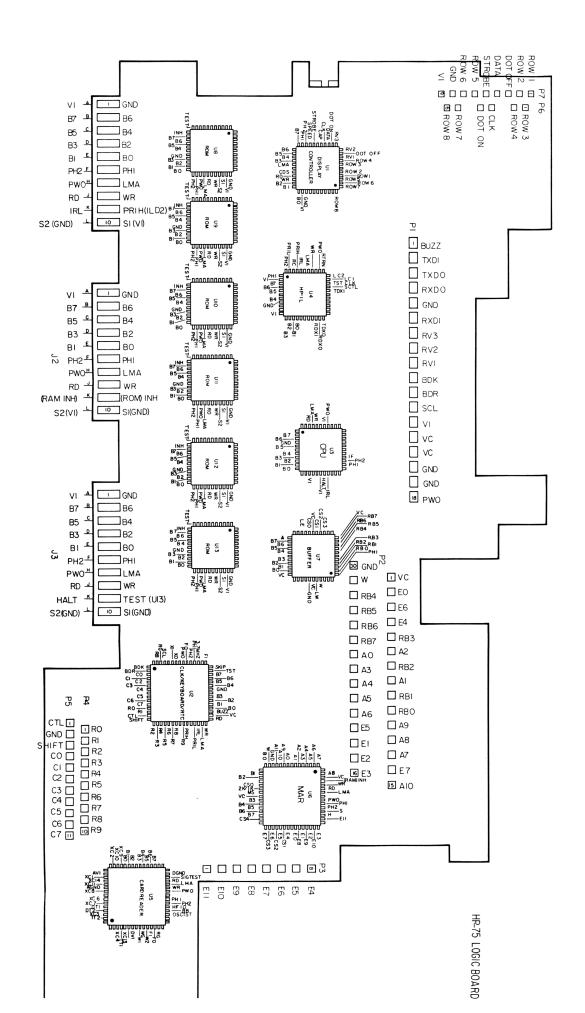

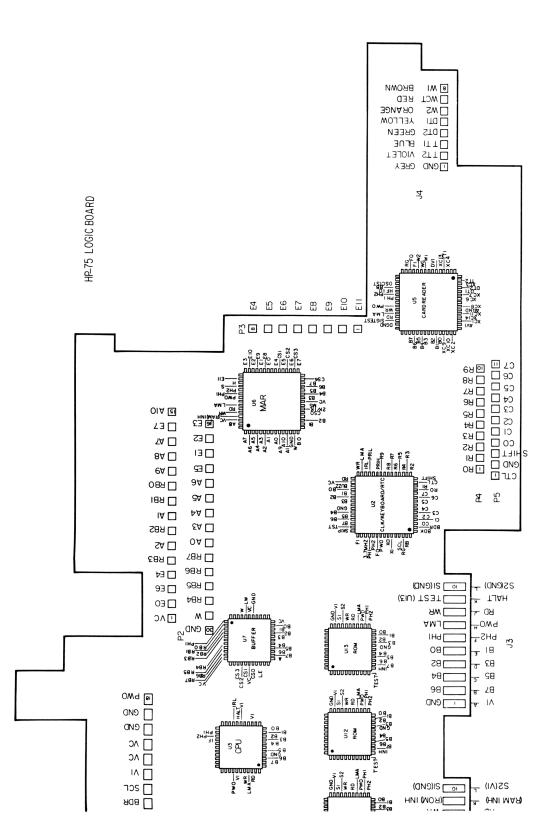

#### 2-5. The logic PCA (printed-circuit assembly) (A2) contains the following:

o CPU IC (integrated circuit) (U3).

o Clock/Keyboard/RTC IC (U2).

o Six system ROM ICs (U8 through U13).

o MAR IC (memory-address register) (U6).

o Buffer IC (U7).

o HP-IL IC (U4).

o Card reader IC (U5).

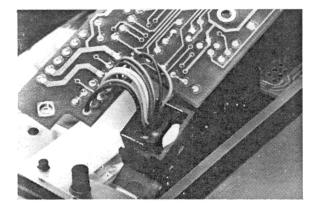

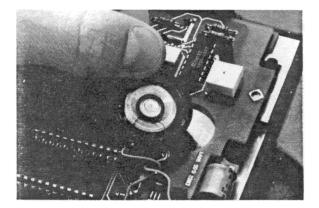

o Card-reader head assembly.

o Display controller IC (U1).

2-6. The display assembly (A3) contains the following:

o Seven display driver ICs (U1 through U7).

o 32-character (apparent 5x9 dot matrix) LCD.

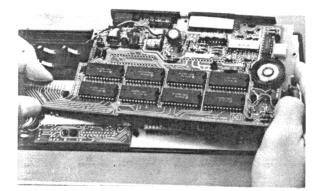

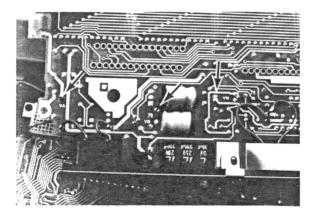

2-7. The power supply/memory PCA (A1) contains the following:

o Dc-to-dc converter.

o Battery level detect.

o Battery charger circuit.

o Generator for the display reference voltages.

o Buzz circuit.

o Automatic reset circuit.

o 16K of RAM.

o 8K memory module connector.

o HP-IL interfacing.

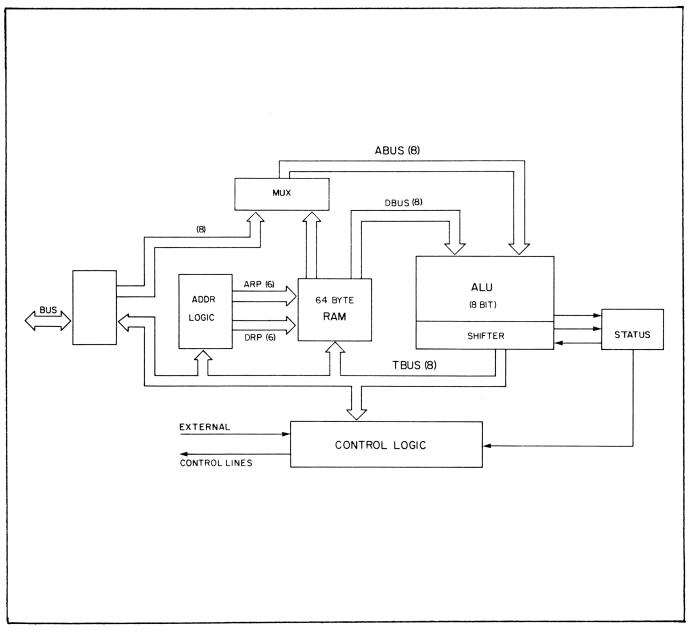

#### 2-8. CPU

2-9. The CPU (see figure 2-2) used in the HP-75 was designed to ease the software task in developing calculator type products. The CPU can uniquely address 65,536 bytes of memory (16-bit address). It has multilevel vectored interrupt capability and allows a crude form of direct memory access (DMA). It also contains 64 general-purpose eight-bit registers. Binary and decimal arithmetic and shift operations can be easily performed. To simplify multibyte arithmetic operations and allow string manipulations, the CPU performs instructions that operate on data one to eight bytes in length.

Figure 2-2. CPU Block Diagram

2-10. When the CPU branches to a subroutine or a program call, the CPU stores the return address in a stack that the CPU creates in RAM. The stack is controlled by a stack pointer in a CPU register (see figure 2-3). Because the return address is stored in RAM, the CPU can handle an almost unlimited nesting of subroutines and program calls. Any of the CPU register pairs can be used as a stack pointer. Both direct and indirect operations can be performed on both increasing and decreasing stacks.

Figure 2-3. CPU Register Diagram

Theory of Operation

2-11. An eight-bit bus handles all communication with the other ICs. This eight-bit multiplexed bus transports data, instructions, and addresses. When more than one byte of data is sent on the bus, an address is needed only for the first byte. The remaining data is assumed to be in consecutive memory locations. Therefore, the bus primarily moves data and instructions while minimizing the movement of addresses. Signal names are listed in table 2-1.

2-12. The memory in the HP-75 handles the implementation of this method by incrementing the address register upon receiving a read or write command. Also, the instruction-fetch sequence does not require an updated address when fetching from most consecutive locations.

2-13. RAM

2-14. The RAM in the HP-75 is fabricated in CMOS (complentary metal-oxidesemiconductor). This process allows the RAM to retain its contents when the CPU is inactive and the power supply is in its powered-down state. While the computer is off, a fully charged battery pack can retain the contents of the RAM for at least two months. A capacitor inside the computer allows the user at least 30 seconds to change the batteries without losing the contents of the RAM, providing the computer is first turned off.

2-15. The HP-75 has the capability of supporting up to 24K bytes of RAM. The HP-75C has eight RAM ICs, which are fabricated in a 2K x 8-bit structure, for a total of 16K bytes of RAM. The computer is allowed to accept an 8K byte plug-in memory module to expand the allotted memory to 24K. The HP-75's internal operating system checks memory at turn on to determine if there is a plug-in memory module.

2-16. Two ICs interface the CPU's bus to the RAM. The memory address controller (MAR) and the buffer function together as one unit.

2-17. MAR

2-18. The primary functions of the MAR IC are:

o Holds the 16-bit current memory address.

o Accepts a new address from data bus as two sequential bytes.

o Increments the address after each memory access (except I/O accesses).

o Drives IC select and address lines for the RAM ICs.

o Selectively activates 12 memory IC enables.

o Drives read/write control line for RAM ICs.

| AO-A11Address output lines to RAMAGNDAnalog groundAVIAnalog intermittent power supplyBBank select, brought out to center portBO-B7System data bus lines, valid during PH1BDKBattery K detect lineBDRBattery R detect lineBUZZSpeaker control lineCO-C25Column outputs used to drive LCD, on display PCA onlCO-C7Keyboard column linesCAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DATAData, sends data to display driversDATA INSerial data input | SIGNAL   | DESCRIPTION                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------|

| AVIAnalog intermittent power supplyBBank select, brought out to center portBO-B7System data bus lines, valid during PH1BDKBattery K detect lineBDRBattery R detect lineBUZZSpeaker control lineCO-C25Column outputs used to drive LCD, on display PCA onlCO-C7Keyboard column linesCAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DATAData, sends data to display drivers                                                                           | AO-A11   | Address output lines to RAM                           |

| BBank select, brought out to center portBO-B7System data bus lines, valid during PH1BDKBattery K detect lineBDRBattery R detect lineBUZZSpeaker control lineCO-C25Column outputs used to drive LCD, on display PCA onCO-C7Keyboard column linesCAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DATAData, sends data to display drivers                                                                                                               | AGND     | Analog ground                                         |

| B0-B7System data bus lines, valid during PH1BDKBattery K detect lineBDRBattery R detect lineBUZZSpeaker control lineC0-C25Column outputs used to drive LCD, on display PCA onlC0-C7Keyboard column linesCAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                      | AVI      | Analog intermittent power supply                      |

| BDKBattery K detect lineBDRBattery R detect lineBUZZSpeaker control lineCO-C25Column outputs used to drive LCD, on display PCA onlCO-C7Keyboard column linesCAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                                                  | В        | Bank select, brought out to center port               |

| BDRBattery R detect lineBUZZSpeaker control lineCO-C25Column outputs used to drive LCD, on display PCA onlCO-C7Keyboard column linesCAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DOT OFFDot off, turns dots off in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                               | B0-B7    | System data bus lines, valid during PH1               |

| BUZZSpeaker control lineC0-C25Column outputs used to drive LCD, on display PCA onlocationC0-C7Keyboard column linesCAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DOT OFFDot off, turns dots off in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                                                | BDK      | Battery K detect line                                 |

| CO-C25Column outputs used to drive LCD, on display PCA onlCO-C7Keyboard column linesCAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DOT OFFDot off, turns dots off in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                                                                               | BDR      | Battery R detect line                                 |

| CO-C7Keyboard column linesCAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DOT OFFDot off, turns dots off in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                                                                                                                                         | BUZZ     | Speaker control line                                  |

| CAPInternal oscillator, frequency set by capacitor.CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DOT OFFDot off, turns dots off in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                                                                                                                                                                   | CO-C25   | Column outputs used to drive LCD, on display PCA only |

| CDSAddress code select, used to determine I/O addressCLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DOT OFFDot off, turns dots off in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                                                                                                                                                                                                                      | C0-C7    | Keyboard column lines                                 |

| CLKClock, clocks data from A2U1 to A3U1-A3U7CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DOT OFFDot off, turns dots off in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                                                                                                                                                                                                                                                                           | CAP      | Internal oscillator, frequency set by capacitor.      |

| CS1-CS3Chip select, 8K address space enableCTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DOT OFFDot off, turns dots off in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CDS      | Address code select, used to determine I/O address    |

| CTLControl keyboard lineDOT ONDot on, turns dots on in A3U1-A3U7DOT OFFDot off, turns dots off in A3U1-A3U7DATAData, sends data to display drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CLK      | Clock, clocks data from A2U1 to A3U1-A3U7             |